## **MORNSUN**<sup>®</sup>

### TDA51S-41HC SOIC package integrated isolated DC-DC converter

#### Features

- Ultra-small, ultra-thin, chip scale SOIC package

- · Baud rate up to 100Mbps

- Wide input supply range: 3.15 V to 5.5 V

- High isolation to 5000Vrms

- Nanosecond propagation delay •

- Integrated overload, short-circuit protection and thermal shutdown •

- High CMTI: 150 kV/µs (typical)

- Industrial operating ambient temperature range: -40  $^\circ\!\mathrm{C}$  to +125  $^\circ\!\mathrm{C}$

- RoHS-Compliant Packages: SOIC16-WB

#### Applications

- 3.3V/5V conversion

- Bus isolated communication

- Isolated sensor interface

- Industrial automation systems

- Motor control

- Medical isolated .

- Test and measurement

- Isolated ADC, DAC

#### **Functional Description**

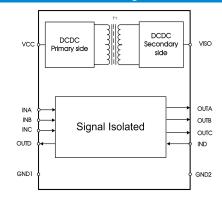

TDA51S-41HC is a family of high-performance reinforced digital isolators with an integrated isolated DC-DC converter. TDA51S-41HC eliminate the need for a separate, isolated power supply, which results in a small form factor, total isolation solution.

TDA51S-41HC device has three forward and one reverse-direction channels, and it has fail-safe mode option. If the input signal is lost, default output is low for devices with H. In addition, other channel communication types, such as two forward channels and two reverse channels, four forward channels, four reverse channels, and many other channel combination types are under development.

MORNSUN Guangzhou Science & Technology Co., Ltd.

2023.10.26-A/4 MORNSUN Guangzhou Science & Technology Co., Ltd. reserves the copyright and right of final interpretation

Package

Page 1 of 10

| 1 | Home  | 2                                | 1 |

|---|-------|----------------------------------|---|

|   | 1.1   | Feature and Package              | 1 |

|   | 1.2   | Applications                     | 1 |

|   | 1.3   | Functional Description           | 1 |

| 2 | Pin C | onnection and Description        | 2 |

| 3 | IC Re | elated Parameters                | 3 |

|   | 3.1   | Absolute Maximum Rating          | 3 |

|   | 3.2   | Recommended Operating Conditions | 3 |

|   | 3.3   | Electrical Characteristics       | 4 |

#### Pin Connection

| VCC 1<br>GND1 2<br>INA 3<br>INB 4<br>INC 5<br>OUTD 6<br>NC 7<br>GND1 8 | TDA51S-41HC | 16       VISO         15       GND2         14       OUTA         13       OUTB         12       OUTC         11       IND         10       SEL         9       GND2 |

|------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                        |             |                                                                                                                                                                      |

Note: All GND1 pins are internally connected; All GND2 pins are internally connected.

#### Function Table

# 3.5 Transmission Information 6 3.6 Physical Information 6 4 Test Circuits 6 5 Product Working Description 7 6 Application Circuit 7 7 Order Information 8 8 Package Information 8 9 Tape & Reel Information 9

#### Internal Block Diagram

| SEL Input                   | Vcc  | Viso |

|-----------------------------|------|------|

| Shorted to VISO             | 5V   | 5V   |

| Shorted to GND2 or floating | 5V   | 3.3V |

| Shorted to GND2 or floating | 3.3V | 3.3V |

#### Note:

1.  $V_{CC}$  = 3.3 V, SEL shorted to VISO ( $V_{ISO}$  = 5 V) is not recommended mode of configuration.

2. The SEL pin has a weak pulldown internally. For VISO = 3.3 V, the SEL pin should be strongly connected to the GND2 pin in noisy system scenarios.

#### Table 2. Operation Mode Table

| Vcc | Input | Output       | Operation                                                                                                       |

|-----|-------|--------------|-----------------------------------------------------------------------------------------------------------------|

|     | Н     | Н            | Normal operation mode:                                                                                          |

| PU  | L     | L            | A channel's output follows the input state                                                                      |

|     | Open  | Default      | Default output fail-safe mode:<br>If a channel's input is left open, its output goes to the default high level. |

| PD  | Х     | Undetermined |                                                                                                                 |

#### Note:

1. PU = Powered up (V<sub>CC</sub>  $\geq$  2.7 V); PD = Powered down (V<sub>CC</sub>  $\leq$  2.1 V); X = Irrelevant; H = High level; L = Low level.

2. The outputs are in undetermined state when  $V_{CC}$  < 2.1V.

MORNSUN Guangzhou Science & Technology Co., Ltd.

2023.10.26-A/4 Page 2 of 10

| Pin Number | Pin Name         | Pin Functions                                                                                              |

|------------|------------------|------------------------------------------------------------------------------------------------------------|

| 1          | Vcc              | Power supply(Side 1) By using 0.1uF and 22uF ceramic capacitance GND1                                      |

| 2          | GND1             | Ground(Side 1)                                                                                             |

| 3          | INA              | Digital input(Side 1)                                                                                      |

| 4          | INB              | Digital input(Side 1)                                                                                      |

| 5          | INC              | Digital input(Side 1)                                                                                      |

| 6          | OUTD             | Digital output(Side 1)                                                                                     |

| 7          | NC               | No Connect.                                                                                                |

| 8          | GND1             | Ground(side 1)                                                                                             |

| 9          | GND <sub>2</sub> | Ground(Side 2)                                                                                             |

| 10         | SEL              | VISO selection pin                                                                                         |

| 11         | IND              | Digital input(Side 2)                                                                                      |

| 12         | OUTC             | Digital output(Side 2)                                                                                     |

| 13         | OUTB             | Digital output(Side 2)                                                                                     |

| 14         | OUITA            | Digital output(Side 2)                                                                                     |

| 15         | GND <sub>2</sub> | Ground(Side 2)                                                                                             |

| 16         | V <sub>ISO</sub> | Isolated output supply voltage determined by SEL pin. By using 0.1uF and 47uF ceramic capacitance Ground2. |

Note: VISO selection pin.  $V_{ISO}$  = 5 V when SEL is connected to VISO.  $V_{ISO}$  = 3.3 V, when SEL is connected to GND2 or left floating.

#### Absolute Maximum Ratings

General test conditions: Free-air, normal operating temperature range (unless otherwise specified).

| Parameters                    | Unit                           |

|-------------------------------|--------------------------------|

| Supply voltage Vcc            | -0.5V to +6V                   |

| Input voltage V <sub>in</sub> | -0.5V to V <sub>CC</sub> +0.5V |

| Output current Io             | -20mA to +20mA                 |

| Receiver Output current TJ    | < 150°C                        |

| Operating temperature range   | -40°C to +125°C                |

| Storage temperature range     | -65°C to +150°C                |

Important: Exposure to absolute maximum rated conditions for an extended period may severely affect the device reliability, and stress levels exceeding the "Absolute Maximum Ratings" may result in permanent damage.

#### **Recommended Operating Conditions**

|                | Parameters                |                                                                                                                     |     | Тур. | Max. | Unit |  |

|----------------|---------------------------|---------------------------------------------------------------------------------------------------------------------|-----|------|------|------|--|

| Vcc            | Sup                       | 3.15                                                                                                                |     | 5.5  | V    |      |  |

| Vін            | High-lev                  | vel Input Voltage                                                                                                   | 2   |      |      | V    |  |

| VIL            | Low-lev                   | el Input Voltage                                                                                                    |     |      | 0.8  | V    |  |

| 1              | Link land Output Ourput   | V <sub>CCO</sub> =5V                                                                                                | -4  |      |      | — mA |  |

| Іон            | High-level Output Current | V <sub>CCO</sub> =3.3V                                                                                              | -2  |      |      |      |  |

| 1              |                           | V <sub>CCO</sub> =5V                                                                                                |     |      | 4    |      |  |

| Iol            | Low-level Output Current  | V <sub>CCO</sub> =3.3V                                                                                              |     |      | 2    | - mA |  |

| TA             | Ambie                     | nt Temperature                                                                                                      | -40 |      | 125  | °C   |  |

| P <sub>D</sub> | Maximum Power Dissipation | Vcc= 5.5V, V <sub>ISO</sub> = 5.5V, I <sub>LOAD</sub> =130mA,<br>all digital channels input :f=100MHz ;<br>Duty=50% |     |      | 1    | w    |  |

| DR             | [                         | Data Rate                                                                                                           |     |      | 100  | Mbps |  |

Note:  $V_{CCI}$  = signal input side supply;  $V_{CCO}$  = signal output side supply.

MORNSUN Guangzhou Science & Technology Co., Ltd.

2023.10.26-A/4 Page 3 of 10

#### 5 V Input, 5 V output : Vcc= 5 V $\pm$ 10%, T<sub>A</sub>= -40 to 125°C, SEL shorted to Viso

|                       | Parameters                                                                | Conditions                                                                 | Min.                      | Тур.                      | Max. | Unit  |

|-----------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------|---------------------------|------|-------|

| V                     |                                                                           | External I <sub>ISO</sub> =0 to 50mA                                       | 4.75                      | 5.07                      | 5.43 | v     |

| V <sub>ISO</sub>      | Isolated supply voltage                                                   | External I <sub>ISO</sub> =0 to 130mA                                      | 4.5                       | 5.07                      | 5.43 | v     |

| VISO(LINE)            | DC line regulation                                                        | $I_{\rm ISO} {=} 50 mA$ , $V_{\rm CC} {=} 4.5 V$ to $5.5 V$                |                           | 2                         |      |       |

| VISO(LOAD)            | DC load regulation                                                        | I <sub>ISO</sub> =0 to 130mA                                               |                           | 1%                        |      |       |

| EFF                   | Efficiency at maximum load current                                        | I <sub>ISO</sub> =130mA,C <sub>L</sub> =0.1uF  10uF;<br>V <sub>I</sub> =0V |                           | 53%                       |      |       |

| VCC(UVLO+)            | V <sub>CC</sub> under voltage threshold when<br>supply voltage is rising  |                                                                            |                           | 2.7                       |      | V     |

| VCC(UVLO-)            | V <sub>CC</sub> under voltage threshold when<br>supply voltage is falling |                                                                            | 2.1                       |                           |      | V     |

| VHYS(UVLO)            | $V_{\mbox{\scriptsize CC}}$ under voltage threshold hysteresis            |                                                                            |                           | 0.2                       |      | V     |

| Ін                    | High-level input leakage current                                          | VIH=VCCI at INx                                                            |                           |                           | 20   | uA    |

| lı.                   | Low-level input leakage current                                           | Vı∟ = 0V at INx                                                            | -20                       |                           |      | uA    |

| Vон                   | High-level output voltage                                                 | Iон = –4 mA, Figure 8                                                      | V <sub>cco</sub> –<br>0.4 | V <sub>cco</sub> –<br>0.2 |      | V     |

| Vol                   | Low-level output voltage                                                  | IoL = 4 mA, Figure 8                                                       |                           | 0.2                       | 0.4  | V     |

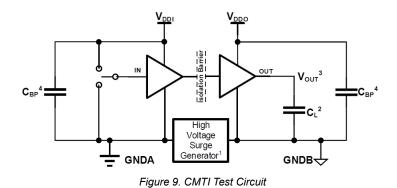

| CMTI                  | Common-mode transient immunity                                            | $V_1 = 0 V \text{ or VCC}$ , Figure 9                                      | 100                       | 150                       |      | kV/us |

| I <sub>scc_sc</sub>   | DC current from supply under short<br>circuit on V <sub>ISO</sub>         | $V_{\text{ISO}}$ shorted to GND2                                           |                           | 42                        |      | mA    |

| V <sub>ISO(RIP)</sub> | Output ripple on isolated supply (pk-pk)                                  |                                                                            |                           | 60                        |      | mV    |

#### 5 V Input, 3.3 V output : Vcc= 5 V $\pm$ 10%, T<sub>A</sub> = -40 to 125°C, SEL shorted to GND2

|            | Parameters                                                                | Conditions                                           | Min.                      | Тур.                      | Max. | Unit  |

|------------|---------------------------------------------------------------------------|------------------------------------------------------|---------------------------|---------------------------|------|-------|

| N/         |                                                                           | External I <sub>ISO</sub> =0 to 50mA                 | 3.13                      | 3.34                      | 3.56 | N     |

| Viso       | Isolated supply voltage                                                   | External I <sub>ISO</sub> =0 to 130mA                | 3                         | 3.34                      | 3.56 | V     |

| VISO(LINE) | DC line regulation                                                        | $I_{\rm ISO}{=}50mA$ , $V_{\rm CC}{=}4.5V$ to $5.5V$ |                           | 2                         |      |       |

| VISO(LOAD) | DC load regulation                                                        | I <sub>ISO</sub> =0 to 130mA                         |                           | 1%                        |      |       |

| EFF        | Efficiency at maximum load current                                        | I <sub>ISO</sub> =130mA,C∟=0.1uF  10uF;<br>Vi=0V     |                           | 48%                       |      |       |

| VCC(UVLO+) | V <sub>CC</sub> under voltage threshold when<br>supply voltage is rising  |                                                      |                           | 2.7                       |      | V     |

| Vcc(uvlo-) | V <sub>CC</sub> under voltage threshold when<br>supply voltage is falling |                                                      | 2.1                       |                           |      | V     |

| VHYS(UVLO) | $V_{\mbox{\scriptsize CC}}$ under voltage threshold hysteresis            |                                                      |                           | 0.2                       |      | V     |

| Ін         | High-level input leakage current                                          | VIH=VCCI at INx                                      |                           |                           | 20   | uA    |

| lı∟        | Low-level input leakage current                                           | V <sub>IL</sub> = 0V at INx                          | -20                       |                           |      | uA    |

| Vон        | High-level output voltage                                                 | Іон <b>= –4 mA</b> , Figure 8                        | V <sub>CCO</sub> –<br>0.4 | V <sub>CCO</sub> –<br>0.2 |      | V     |

| Vol        | Low-level output voltage                                                  | lo∟ = 4 mA, Figure 8                                 |                           | 0.2                       | 0.4  | V     |

| CMTI       | Common-mode transient immunity                                            | $V_1 = 0 V \text{ or VCC}$ , Figure 9                | 100                       | 150                       |      | kV/us |

| lscc_sc    | DC current from supply under short circuit on V <sub>ISO</sub>            | VISO shorted to GND2                                 |                           | 38                        |      | mA    |

| VISO(RIP)  | Output ripple on isolated supply (pk-pk)                                  |                                                      |                           | 58                        |      | mV    |

#### 3.3 V Input, 3.3 V output : Vcc= 3.3V $\pm$ 5%, T<sub>A</sub>= -40 to 125°C, SEL shorted to GND2

|                  | Parameters                                                               | Conditions                                                                          | Min. | Тур. | Max. | Unit |

|------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------|------|------|------|

| N                |                                                                          | External I <sub>ISO</sub> =0 to 50mA                                                | 3.13 | 3.34 | 3.56 | N    |

| V <sub>ISO</sub> | Isolated supply voltage                                                  | External I <sub>ISO</sub> =0 to 75mA                                                | 3    | 3.34 | 3.56 | V    |

| VISO(LINE)       | DC line regulation                                                       | $I_{\rm ISO}\text{=}50\text{mA}$ , $V_{\rm CC}\text{=}4.5\text{V}$ to $5.5\text{V}$ |      | 2    |      |      |

| VISO(LOAD)       | DC load regulation                                                       | I <sub>ISO</sub> =0 to 130mA                                                        |      | 1%   |      |      |

| EFF              | Efficiency at maximum load current                                       | I <sub>ISO</sub> =130mA,C <sub>L</sub> =0.1uF  10uF;<br>V <sub>I</sub> =0V          |      | 47%  |      |      |

| VCC(UVLO+)       | V <sub>CC</sub> under voltage threshold when<br>supply voltage is rising |                                                                                     |      |      | 2.7  | V    |

**MORNSUN®**

MORNSUN Guangzhou Science & Technology Co., Ltd.

|            | Parameters                                                                | Conditions                            | Min.                      | Тур.                      | Max. | Unit  |

|------------|---------------------------------------------------------------------------|---------------------------------------|---------------------------|---------------------------|------|-------|

| VCC(UVLO-) | V <sub>CC</sub> under voltage threshold when<br>supply voltage is falling |                                       | 2.1                       |                           |      | V     |

| VHYS(UVLO) | Vcc under voltage threshold hysteresis                                    |                                       |                           | 0.2                       |      | V     |

| Ін         | High-level input leakage current                                          | VIH=VCCI at INx                       |                           |                           | 20   | uA    |

| ١L         | Low-level input leakage current                                           | V <sub>IL</sub> = 0V at INx           | -20                       |                           |      | uA    |

| Vон        | High-level output voltage                                                 | Іон <b>= –4 mA</b> , Figure 8         | V <sub>cco</sub> –<br>0.4 | V <sub>cco</sub> –<br>0.2 |      | V     |

| Vol        | Low-level output voltage                                                  | lo∟ = 4 mA, Figure 8                  |                           | 0.2                       | 0.4  | V     |

| CMTI       | Common-mode transient immunity                                            | $V_1 = 0 V \text{ or VCC}$ , Figure 9 | 100                       | 150                       |      | kV/us |

| lscc_sc    | DC current from supply under short<br>circuit on V <sub>ISO</sub>         | V <sub>ISO</sub> shorted to GND2      |                           | 32                        |      | mA    |

| VISO(RIP)  | Output ripple on isolated supply (pk-pk)                                  |                                       |                           | 55                        |      | mV    |

Note: V<sub>CCI</sub> = signal input side supply; V<sub>CCO</sub> = signal output side supply.

#### Supply Current Characteristics

#### 5 V Input, 5 V output : Vcc= 5 V $\pm$ 10%, T<sub>A</sub> = -40 to 125°C, SEL shorted to V<sub>ISO</sub>

|           | Parameters                              | Conditions                                                                  | Min. | Тур. | Max. | Unit |

|-----------|-----------------------------------------|-----------------------------------------------------------------------------|------|------|------|------|

|           |                                         | No external ILOAD ; VI=0V                                                   |      | 23   |      |      |

|           |                                         | No external I <sub>LOAD</sub> ; V <sub>I</sub> =V <sub>CCI</sub>            |      | 17   |      |      |

| lcc       | Current drawn from                      | All channels switching : f=1Mbps,<br>Duty=50%; CL=15pF, No external ILOAD   |      | 20   |      | mA   |

|           | supply                                  | All channels switching : f=10Mbps,<br>Duty=50%; CL=15pF, No external ILOAD  |      | 24   |      |      |

|           |                                         | All channels switching : f=100Mbps,<br>Duty=50%; CL=15pF, No external ILOAD |      | 54   |      |      |

|           |                                         | No external ILOAD ; VI=0V                                                   |      |      | 128  |      |

|           |                                         | No external I <sub>LOAD</sub> ; V <sub>I</sub> =V <sub>CCI</sub>            |      |      | 130  |      |

| IISO(OUT) | Current available to<br>isolated supply | All channels switching : f=1Mbps,<br>Duty=50%; CL=15pF, No external ILOAD   |      |      | 128  | mA   |

|           | All channels switching : f=10Mbp        | All channels switching : f=10Mbps,<br>Duty=50%; CL=15pF, No external ILOAD  |      |      | 127  |      |

|           |                                         | All channels switching : f=100Mbps,<br>Duty=50%; CL=15pF, No external ILOAD |      |      | 112  |      |

#### 5 V Input, 3.3 V output : Vcc= 5V $\pm$ 10%, T<sub>A</sub> = -40 to 125°C, SEL shorted to GND2

|           | Parameters                              | Conditions                                                                       | Min. | Тур. | Max. | Unit |

|-----------|-----------------------------------------|----------------------------------------------------------------------------------|------|------|------|------|

| Icc       |                                         | No external ILOAD ; VI=0V                                                        |      | 23   |      |      |

|           |                                         | No external I <sub>LOAD</sub> ; V <sub>I</sub> =V <sub>CCI</sub>                 |      | 14   |      |      |

|           | Current drawn from                      | All channels switching : f=1Mbps,<br>Duty=50%; CL=15pF, No external ILOAD        |      | 17   |      | mA   |

|           | supply                                  | All channels switching : f=10Mbps, Duty=50%; $C_L$ =15pF, No external $I_{LOAD}$ |      | 20   |      |      |

|           |                                         | All channels switching : f=100Mbps, Duty=50%; CL=15pF, No external $I_{LOAD}$    |      | 40   |      |      |

| liso(out) |                                         | No external $I_{LOAD}$ ; $V_I=0V$                                                |      |      | 128  |      |

|           |                                         | No external I <sub>LOAD</sub> ; V <sub>I</sub> =V <sub>CCI</sub>                 |      |      | 130  |      |

|           | Current available to<br>isolated supply | All channels switching : f=1Mbps,<br>Duty=50%; CL=15pF, No external $I_{LOAD}$   |      |      | 129  | mA   |

|           |                                         | All channels switching : f=10Mbps,<br>Duty=50%; CL=15pF, No external ILOAD       |      |      | 128  |      |

|           |                                         | All channels switching : f=100Mbps,<br>Duty=50%; CL=15pF, No external ILOAD      |      |      | 118  |      |

#### 3.3 V Input, 3.3 V output : Vcc= 3.3V $\pm$ 5%, T<sub>A</sub>= -40 to 125°C, SEL shorted to GND2

| Parameters |                    | Conditions                                                                                         | Min. | Тур. | Max. | Unit |

|------------|--------------------|----------------------------------------------------------------------------------------------------|------|------|------|------|

|            |                    | No external ILOAD ; VI=0V                                                                          |      | 25   |      |      |

|            | Current drawn from | No external ILOAD ; VI=VCCI                                                                        |      | 17   |      |      |

| Icc        | supply             | All channels switching : f=1Mbps,<br>Duty=50%; C <sub>L</sub> =15pF, No external I <sub>LOAD</sub> |      | 21   |      | mA   |

|            |                    | All channels switching : f=10Mbps,<br>Duty=50%; CL=15pF, No external ILOAD                         |      | 24   |      |      |

**MORNSUN®**

MORNSUN Guangzhou Science & Technology Co., Ltd.

|           | Parameters           | Conditions                                                                        | Min. | Тур. | Max.           | Unit |

|-----------|----------------------|-----------------------------------------------------------------------------------|------|------|----------------|------|

|           |                      | All channels switching : f=100Mbps, Duty=50%; $C_L$ =15pF, No external $I_{LOAD}$ |      | 48   |                |      |

|           |                      | No external ILOAD ; VI=0V                                                         |      |      | 73             |      |

|           |                      | No external I <sub>LOAD</sub> ; V <sub>I</sub> =V <sub>CCI</sub>                  |      |      | 75<br>75<br>74 |      |

| IISO(OUT) | Current available to | All channels switching : f=1Mbps,<br>Duty=50%; CL=15pF, No external ILOAD         |      |      |                | mA   |

|           | isolated supply      | All channels switching : f=10Mbps,<br>Duty=50%; CL=15pF, No external $I_{LOAD}$   |      |      | 73             |      |

|           |                      | All channels switching : f=100Mbps,<br>Duty=50%; CL=15pF, No external $I_{LOAD}$  |      |      | 61             |      |

Note:

1.V<sub>CCI</sub> = signal input side supply; V<sub>CCO</sub> = signal output side supply.

2. When  $T_A > 115^{\circ}$ C, Current available to isolated supply should be reduced by 2mA/°C.

#### Transmission Characteristics General test conditions and Vcc=V10= 5V, Ta = 25°C (unless otherwise specified).

|                                     | Parameters Conditions                                        |             | Min. | Тур. | Max. | Unit |

|-------------------------------------|--------------------------------------------------------------|-------------|------|------|------|------|

| DR                                  | Data Rate                                                    | Data Rate 0 |      |      | 100  | Mbps |

| $PW_{minL}$                         | Minimum Pulse Width                                          |             |      |      | 5.0  | ns   |

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation Delay Time                                       |             | 6.0  | 10.0 | 15.0 | ns   |

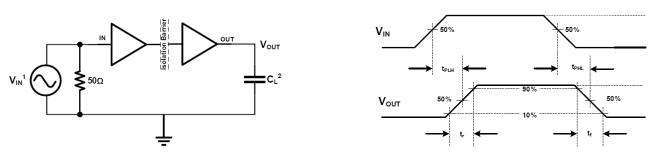

| PWD                                 | Pulse Width Distortion   t <sub>PLH</sub> - t <sub>PHL</sub> | Figure 8    |      | 0.2  | 4.5  | ns   |

| t <sub>rk(O)</sub>                  | Channel-to-channel Output Skew<br>Time                       | -           |      | 0.4  | 2.5  | ns   |

| t <sub>rk(pp)</sub>                 | Part-to-part Skew Time                                       |             |      | 2.0  | 4.5  | ns   |

| tr                                  | Output Signal Rise Time                                      | Figure 8    |      | 2.5  | 4.0  | ns   |

| t <sub>f</sub>                      | Output Signal Fall Time                                      |             |      | 2.5  | 4.0  | ns   |

Note:

1.t<sub>rk(o)</sub> is the skew between outputs of a single device with all driving inputs connected and the outputs switching in the same direction while driving identical loads.

2.t<sub>rk(pp)</sub> is the magnitude of the difference in propagation delay times between any terminals of different devices switching in the same direction while operating at identical supply voltages, temperature, input signals and loads.

#### Physical Specifications

| Parameters | Value     | Unit |

|------------|-----------|------|

| Weight     | 0.4(Typ.) | g    |

**Test Circuits**

Figure 8. Timing Characteristics Test Circuit and Voltage Wave forms

Note:

1. A square wave generator generate the VIN input signal with the following constraints: waveform frequency  $\leq$  100kHz, 50% duty cycle, t<sub>r</sub> $\leq$  3ns, t<sub>f</sub> $\leq$  3ns. Since the waveform generator has an output impedance of Z<sub>out</sub> = 50 $\Omega$ , the 50 $\Omega$  resistor in the figure is used for matching. There is no need in the actual application.

2. C<sub>L</sub> is the load capacitance about 15pF together with the instrumentation capacitance. Since the load capacitance influence the output rising time, it's a key factor in the timing characteristic measurement.

MORNSUN Guangzhou Science & Technology Co., Ltd.

2023.10.26-A/4 Page 6 of 10

Note:

1. The High Voltage Surge Generator generates repetitive high voltage surges with > 1.5kV amplitude and <10ns rise time and fall time to reach common-mode transient noise with > 150kV/µs slew rate.

2.  $C_L$  is the load capacitance about 15pF together with the instrumentation capacitance.

Pass-fail criteria: The output must remain stable whenever the high voltage surges come.

4. C<sub>BP</sub> is the 0.1 to 1uF bypass capacitance.

#### **Detailed Description**

TDA51S-41HC has a high-efficiency, low-emissions isolated dc-dc converter, with high-speed isolated data channels.

The dc-to-dc converter section of the TDA51S-41HC devices works on principles that are common to most modern power supplies. The devices have a split controller architecture with isolated PWM feedback. VCC power is supplied to an oscillating circuit that switches current into a high-Q on-chip air-core transformer which provide high efficiency and low radiated emissions. The integrated transformer uses thin film polymer as the insulation barrier. Power transferred to the secondary side is rectified and regulated to a value of 3.3 V or 5 V, depending on the setting of the SEL pin. The secondary (VISO) side controller regulates the output by creating a PWM control signal that is sent to the primary side by a dedicated isolated data channel. The PWM modulates the oscillator circuit to control the power being sent to the secondary side. Feedback allows for significantly higher power and efficiency and ensures low overshoots and undershoots during load transients. Undervoltage lockout (UVLO) with hysteresis is integrated on the VCC and VISO supplies which ensures robust system performance under noisy conditions. An integrated soft-start mechanism ensures controlled inrush current and avoids any overshoot on the output during power up. Short-circuit protection: TDA51S-41HC has current-limiting protection to prevent the drive circuit from short-circuiting to positive and negative supply voltages. The power dissipation increases when a short circuit occurs. The short-circuit protection function protects the driver stage from damage.

The high-speed isolated data channels use a simple ON-OFF keying (OOK) modulation scheme to transmit signal across the SiO2 isolation capacitors that provide a robust insulation between two different voltage domain and act as a high frequency signal path between the input and the output. The transmitter (TX) modulates the input signal onto the carrier frequency, that is, TX delivers high frequency signal across the isolation barrier in one input state and delivers no signal across the barrier in the other input state. Then the receiver rebuilds the input signal according to the detected in-band energy. The capacitor-based signal path is fully differential to maximize noise immunity, which is also known as common-mode transient immunity. The capacitively-coupled architecture provides much higher electromagnetic immunity compared to the inductively coupled one.

MORNSUN Guangzhou Science & Technology Co., Ltd.

2023.10.26-A/4 Page 7 of 10

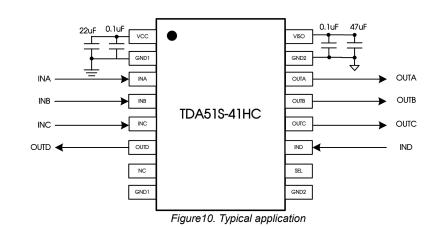

#### PCB Design Instructions

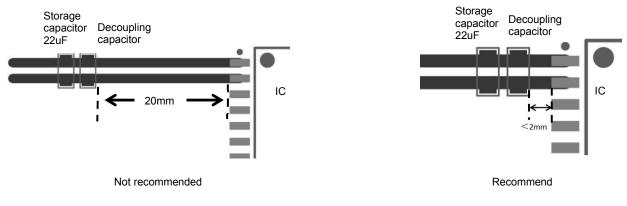

1. The decoupling capacitors and energy storage capacitor of VCC and GND1, VISO and GND2 should be placed as close the chip pins as possible to the chip pins to reduce loop area and parasitic inductance of PCB traces. General control should be within 2mm. The decoupling capacitor is placed close the chip, and the energy storage capacitor is placed outside. As shown in Figre10-1.

2. The power line width should be designed at least 0.5mm when wiring.

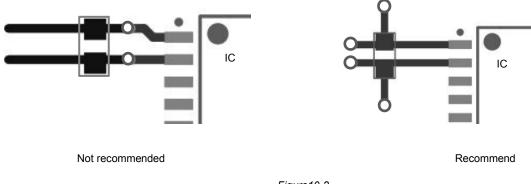

3. When it is necessary to place vias in the power supply line and the ground wire, the position of the vias should be placed on the outside of the capacitor relative to the chip pins ,rather than between the capacitor and the chip, as shown in the figure 10-2 below to reduce the number of vias effect of parasitic inductance.

Figure10-2

MORNSUN Guangzhou Science & Technology Co., Ltd.

#### Design requirement:

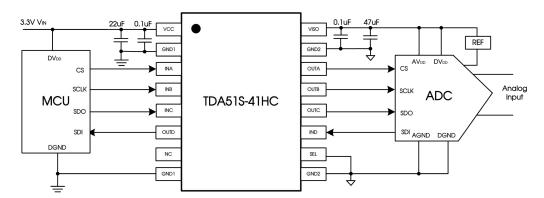

Figure 11. Isolated Power and SPI for ADC Sensing Application with TDA51S-41HC

| Parameter                                                           | Value        |

|---------------------------------------------------------------------|--------------|

| Input voltage V <sub>IN</sub>                                       | 3.0V to 5.5V |

| Decoupling capacitors between $V_{\mbox{cc}}$ and GND1              | 0.1uF, 22uF  |

| Decoupling capacitors between $V_{\mbox{\scriptsize ISO}}$ and GND2 | 0.1uF, 47uF  |

Because of the higher current flowing though the VCC and VISO power supplies of TDA51S-41HC, higher decoupling capacitors usually provide better noise and ripple performance. Although a 10uF capacitor is enough to ensure the normal operation of the product, it is still strongly recommended to use a higher decoupling capacitor( such as 22uF, 47uF) on both VCC and VISO pins to the respective grounds to achieve the best performance.

#### **Ordering Information**

| Part number | Package | Number of pins | Product marking | Tape & Reel |

|-------------|---------|----------------|-----------------|-------------|

| TDA51S-41HC | SOIC    | 16             | TDA51S-41HC     | 1k/REEL     |

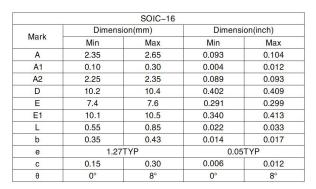

Package Information

THIRD ANGLE PROJECTION 💮 🥣

A

MORNSUN Guangzhou Science & Technology Co., Ltd.

2023.10.26-A/4 Page 9 of 10

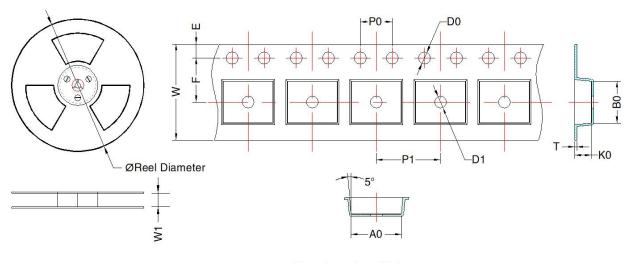

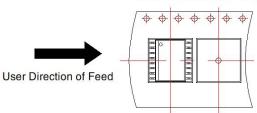

The orientation of IC in tape

| Device      | Package<br>Type | MPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm)     | B0<br>(mm) | K0<br>(mm)    | T<br>(mm)      | W<br>(mm)      | E<br>(mm)      | F<br>(mm)      | P1<br>(mm) | P0<br>(mm) | D0<br>(mm)    | D1<br>(mm)    |

|-------------|-----------------|------|--------------------------|--------------------------|----------------|------------|---------------|----------------|----------------|----------------|----------------|------------|------------|---------------|---------------|

| TDA51S-41HC | SOIC-16         | 1000 | 330.0                    | 16.4                     | $10.9 \pm 0.2$ | 10.7 ± 0.2 | $3.2 \pm 0.2$ | $0.3 \pm 0.05$ | $16.0 \pm 0.3$ | $1.75 \pm 0.1$ | $10.5 \pm 0.1$ | 12.0 ± 0.1 | 4.0 ± 0.1  | $1.5 \pm 0.1$ | $1.5 \pm 0.1$ |

#### MORNSUN Guangzhou Science & Technology Co., Ltd.

Address: No. 5, Kehui St. 1, Kehui Development Center, Science Ave., Guangzhou Science City,HuangpuDistrict, Guangzhou, P. R. ChinaTel: 86-20-38601850Fax: 86-20-38601272E-mail: info@mornsun.cnwww.mornsun-power.com

**MORNSUN®**

MORNSUN Guangzhou Science & Technology Co., Ltd.

2023.10.26-A/4 Page 10 of 10