# SCM3510A Dual Channel Bootstrap Driver

#### **Features**

- Up to 700V withstand voltage

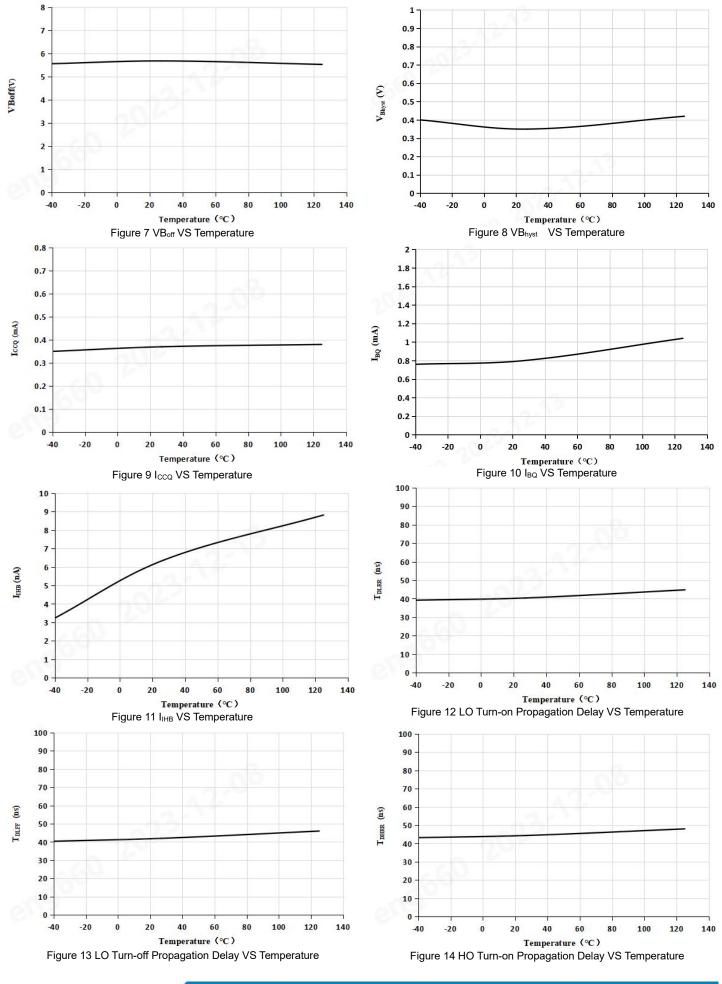

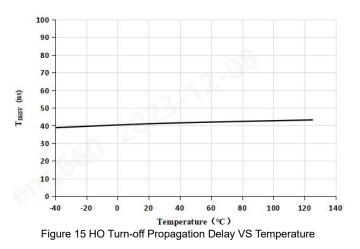

- 40ns typical propagation delay

- · Low quiescent current and operating current

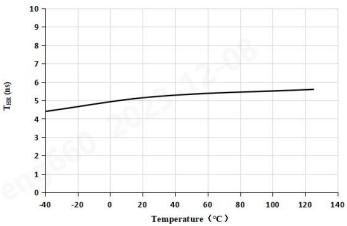

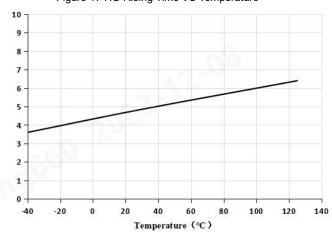

- Wide operating temperature: -40°C~125°C

- Maximum rising and falling time: 15ns

- Dual channel under voltage lockout

- Compatible with 3.3V and 5V input logic

- Up to 100V/ns dV/dt immunity

- Pin compatible with common half-bridges IC in the industry

- Channel matching delay(less than 7ns)

#### **Applications**

- · High-density SMPS for server, telecommunication and industry

- Half-bridge, full-bridge and LLC converter

- · Active clamp flyback/forward converter

- · Solar inverter, Motor control

- · Electric power steering system

# Functional Description

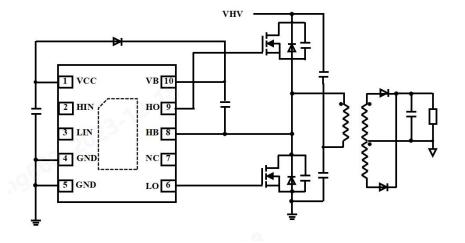

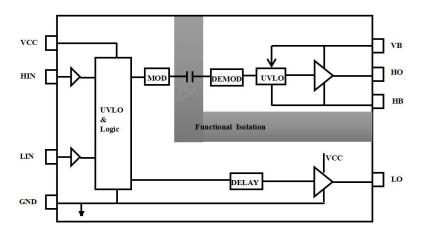

SCM3510A is a high and low sides gate driver which can shift the logic pulse signals received by the HIN and LIN pins to the voltage domain of V<sub>HB</sub>~V<sub>VB</sub>, and then output the corresponding driving signals through the HO, LO pins to control the switch of high and low sides power transistors. In high-voltage bootstrap applications, the pulse signals received by HIN and LIN pins of SCM3510A generally come from the main control chip. The main control chip outputs a duty cycle signal based on the loop control to SCM3510A and then SCM3510A restores the duty cycle signal at the HO and LO pins to control the switch of high and low side power transistors.

#### **Typical Application Circuit**

SCM3510A Typical Application Circuit

#### Package

Mechanical package:LGA4x4-10L (see "Ordering information" for details).

#### **CONTENT**

| FEATURES AND PACKAGING1           | ELECTRICAL CHARACTERISTICS | 3  |

|-----------------------------------|----------------------------|----|

| APPLICATIONS1                     | TRUTH TABLE                | 4  |

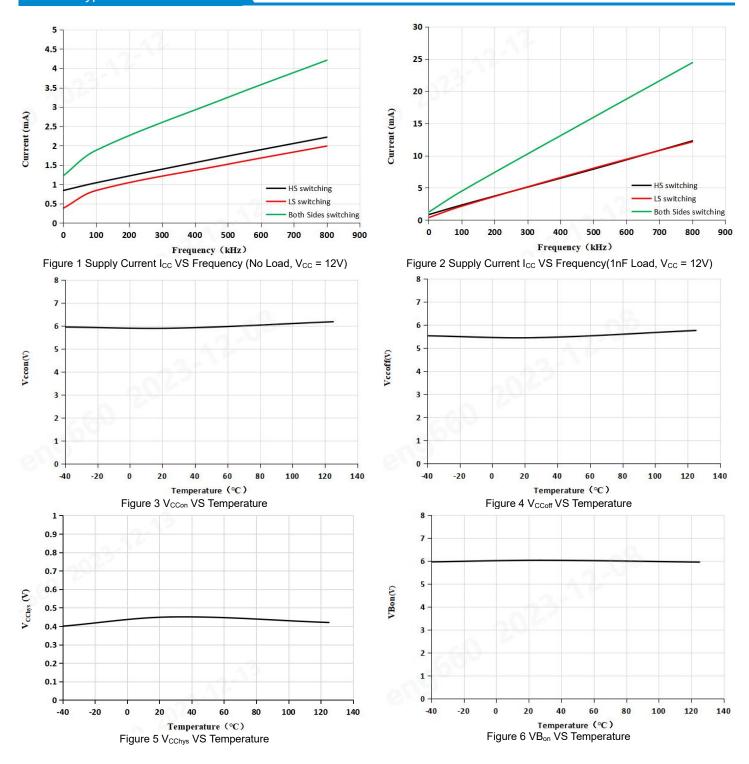

| FUNCTIONAL DESCRIPTION1           | TYPICAL CURVE              | 5  |

| TYPICAL APPLICATION CIRCUIT1      | TEST WAVEFORM              | 8  |

| PIN PACKAGE2                      | OPERATING PRINCIPLE        | 8  |

| INTERNAL BLOCK DIAGRAM2           | USING SUGGESTION           | 9  |

| PIN DESCRIPTION2                  | ORDERING INFORMATION       | 9  |

| ABSOLUTE MAXIMUM RATINGS3         | SCREEN PRINTING            | 10 |

| RECOMMENDED OPERATING CONDITIONS3 | PACKAGE INFORMATIO         | 11 |

| THERMAL CHARACTERISTICS3          | PACKING INFORMATION        | 11 |

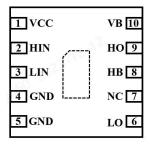

# Pin Package

SCM3510A LGA4x4-10L Pin Package

# Internal Block Diagram

SCM3510A Simplified Circuit Principles

# Pin Description

| Pin Name |     | Functional Description |  |

|----------|-----|------------------------|--|

| 1        | VCC | IC supply voltage      |  |

| 2        | HIN | High side signal input |  |

| 3        | LIN | Low side signal input  |  |

| 4、5      | GND | IC reference ground    |  |

| 6        | LO  | Low side driver output |  |

| 7        | NC  | Not connected          |  |

# **MORNSUN®**

| 8  | НВ | Negative supply of high side driver |

|----|----|-------------------------------------|

| 9  | НО | High side driver output             |

| 10 | VB | Positive supply of high side driver |

### Absolute Maximum Ratings

General test conditions: Ventilation, normal operating temperature range (unless otherwise specified).

| Symbol               | Parameter                                      | Min                  | Max                  | Unit |

|----------------------|------------------------------------------------|----------------------|----------------------|------|

| V <sub>CC</sub>      | Supply voltage V <sub>CC</sub>                 | -0.3                 | 33                   | V    |

| LIN, HIN             | Input signal voltage                           | -5                   | V <sub>CC</sub> +0.3 | V    |

| V <sub>B</sub>       | Voltage of positive supply of high side driver | -0.3                 | 720                  | V    |

| V <sub>HO</sub>      | Voltage of High side driver output             | V <sub>HB</sub> -0.3 | V <sub>B</sub> +0.3  | V    |

| V <sub>LO</sub>      | Voltage of Low side driver output              | -0.3                 | V <sub>CC</sub> +0.3 | V    |

| T <sub>STG</sub>     | Storage temperature                            | -55                  | 150                  | °C   |

| -                    | Reflow temperature                             | -                    | 260                  | °C   |

| TJ                   | Junction temperature                           | -                    | 150                  | °C   |

| dV <sub>нв</sub> /dt | Rate of V <sub>HB</sub> pin change             | -                    | ±100                 | V/ns |

| ESD                  | НВМ                                            | -                    | ±4000                | V    |

| ESD                  | CDM                                            | -                    | ±1500                | V    |

NOTE:

### **Recommended Operating Conditions**

| Symbol                              | Parameter Description                       | Min             | Max            | Unit |

|-------------------------------------|---------------------------------------------|-----------------|----------------|------|

| V <sub>CC</sub>                     | Supply voltage                              | 7               | 25             | V    |

| V <sub>B</sub> -V <sub>HB</sub>     | High side supply floating voltage           | 7               | 25             | V    |

| V <sub>HB</sub>                     | Negative voltage of high side driver supply | -1              | 700            | V    |

| V <sub>HO</sub>                     | Voltage of High side driver output          | V <sub>HB</sub> | V <sub>B</sub> | V    |

| V <sub>LO</sub>                     | Voltage of Low side driver output           | GND             | Vcc            | V    |

| V <sub>LIN</sub> , V <sub>HIN</sub> | Input voltage of high side or low side      | GND             | Vcc-2          | V    |

| T <sub>A</sub>                      | Operating temperature                       | -40             | 125            | °C   |

# Thermal Characteristics

|   | Symbol          | Parameter Description                                           | Value | Unit |

|---|-----------------|-----------------------------------------------------------------|-------|------|

|   | $R_{\theta JA}$ | Junction-to-ambient thermal resistance(LGA4x4-10L) <sup>1</sup> | 162   | °C/W |

| N | OTE:            |                                                                 |       |      |

1.The test values are based on a 50mm<sup>2</sup> copper area with a thickness of 1oz and an FR4 board. Standard JESD51-3 Low Effective Thermal Conductivity Test Board(1s), in an environment

**Electrical Characteristics**

T<sub>A</sub>= -40~+125°C. V<sub>CC</sub> =V<sub>B</sub>=12V, V<sub>HB</sub>=GND, No load, typical values are at Ta=25°C. (unless otherwise noted).

| Symbol           | Parameter                          | Test Condition                         | Min | Тур  | Max  | Unit |

|------------------|------------------------------------|----------------------------------------|-----|------|------|------|

| Supply Ch        | naracteristics                     |                                        |     |      |      |      |

| Iccq             | V <sub>CC</sub> Quiescent Current  | V <sub>LIN</sub> =V <sub>HIN</sub> =0V | -   | 0.5  | 0.6  | mA   |

| Icco             | V <sub>CC</sub> Operating Current  | f=500kHz, C <sub>load</sub> =0         | -   | 2.25 | 2.75 | mA   |

| I <sub>BQ</sub>  | High side supply                   | V <sub>LIN</sub> =V <sub>HIN</sub> =0V | -   | 0.9  |      | mA   |

| I <sub>BO</sub>  | High side supply quiescent current | f=500kHz, C <sub>load</sub> =0         | -   | 2.75 | 3.35 | mA   |

| I <sub>IHB</sub> | HB to GND quiescent current        | V <sub>HB</sub> =700V                  | -   | -    | 0.01 | μΑ   |

| Input Cha        | racteristics                       |                                        |     |      |      |      |

| V <sub>HIT</sub> | Input Rising Threshold             | -                                      | 2.1 | 2.7  | 3.1  | V    |

# **MORNSUN®**

MORNSUN Guangzhou Science & Technology Co., Ltd.

<sup>1.</sup> If the stress values listed in the "absolute maximum ratings" table are exceeded, it may cause permanent damage to the devices. Long term operating under extreme rated conditions may affect the reliability of the devices. All voltage values are based on GND reference.

<sup>2.</sup>This series of ICs include ESD protection and is tested using the following methods: ①The ESD human body model is tested according to AEC-Q100-002 (EIA/JESD22-A114). ②The electrostatic discharge test of charged device model(CDM) is carried out in accordance with AEC-Q100-11 (EIA/JESD22-C101E).③Latchup maximum current ≤150 mA, according to JESD78F.

described inJESD51-2a.

| $V_{LIT}$                                  | Input Falling Threshold     | -                                                                           | 1   | 1.4  | 1.8 | V  |

|--------------------------------------------|-----------------------------|-----------------------------------------------------------------------------|-----|------|-----|----|

| V <sub>HI_HYS</sub><br>V <sub>LI HYS</sub> | Input Voltage Hysteresis    | -                                                                           | -   | 1.3  | -   | V  |

| R <sub>IN</sub>                            | Input Pull down Resistance  | V <sub>XIN</sub> =5V                                                        | 100 | 175  | 250 | kΩ |

| Output Ch                                  | naracteristics              |                                                                             |     |      |     |    |

| T <sub>startup</sub>                       | High Side Startup Time      | Time from V <sub>B</sub> >UVLO to the first rising edge of the HO pulse     | -   | -    | 30  | μs |

| Driving Cl                                 | naracteristics              |                                                                             |     |      |     |    |

| Vol                                        | Logic Low Output Voltage    | I <sub>OSNK</sub> =-100mA                                                   | -   | 0.06 | -   | V  |

| VoH                                        | Logic High Output Voltage   | I <sub>OSRC</sub> =100mA, V <sub>OH</sub> =V <sub>CC</sub> -V <sub>LO</sub> | -   | 0.12 | -   | V  |

| RoL                                        | Logic Low Output Resistance | I <sub>OSNK</sub> =-100mA                                                   | -   | 0.6  | -   | Ω  |

| Rон                                        | Logic Low Output Resistance | I <sub>OSRC</sub> =100mA, V <sub>OH</sub> =V <sub>CC</sub> -V <sub>LO</sub> | -   | 1.2  | -   | Ω  |

| Iosrc                                      | Peak Source Current         | Vo=0V                                                                       | -   | 4    | -   | Α  |

| Iosnk                                      | Peak Sink Current           | V <sub>O</sub> =12V                                                         | -   | 6    | -   | Α  |

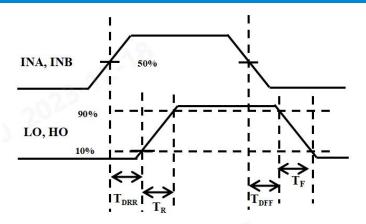

| Output Ri                                  | sing/Falling Time           |                                                                             |     |      |     |    |

| T <sub>R</sub>                             | LO, HO rising time          | C <sub>load</sub> =1nF(10% to 90%)                                          | -   | 8    | 15  | ns |

| T <sub>F</sub>                             | LO, HO falling time         | C <sub>load</sub> =1nF(90% to 10%)                                          | -   | 8    | 15  | ns |

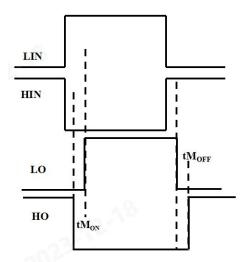

| Channel !                                  | Matching Delay              |                                                                             |     |      |     |    |

| T <sub>MON</sub>                           | LI ON, HI OFF               | Pulse width=1µs                                                             | -   | -    | 7   | ns |

| T <sub>MOFF</sub>                          | LI OFF, HI ON               | Pulse width=1µs                                                             | -   | -    | 7   | ns |

| Minimum                                    | Pulse Width                 |                                                                             | 1   | '    | •   | 1  |

| $PW_{min}$                                 | minimum pulse width         | C <sub>load</sub> =0                                                        | -   | -    | 35  | ns |

| Propagatio                                 | n Delay                     |                                                                             | 1   | 1    | 1   | 1  |

| T <sub>DLRR</sub>                          | LI to LO Turn-on delay      | C <sub>load</sub> =0, Minimum switch Time 50ns                              | -   | 40   | 50  | ns |

| T <sub>DLFF</sub>                          | LI to LO Turn-off delay     | C <sub>load</sub> =0, Minimum switch Time 50ns                              | -   | 40   | 50  | ns |

| T <sub>DHRR</sub>                          | HI to HO Turn-on delay      | C <sub>load</sub> =0, Minimum switch Time 50ns                              | -   | 40   | 50  | ns |

| T <sub>DHFF</sub>                          | HI to HO Turn-off delay     | C <sub>load</sub> =0, Minimum switch Time 50ns                              | -   | 40   | 50  | ns |

SCM3510A(LGA4x4-10L)

| Under volt         | tage Lockout Characteristics           |   |     |      |     |   |

|--------------------|----------------------------------------|---|-----|------|-----|---|

| V <sub>CCon</sub>  | V <sub>CC</sub> UVLO Rising Threshold  | - | 5.6 | 6.25 | 6.9 | V |

| V <sub>CCoff</sub> | V <sub>CC</sub> UVLO Falling Threshold | - | 5.1 | 5.75 | 6.4 | V |

| VcChys             | Vcc UVLO Hysteresis Voltage            | - | -   | 0.5  | -   | V |

| V <sub>Bon</sub>   | V <sub>B</sub> UVLO Rising Threshold   | - | 5.6 | 6.25 | 6.9 | V |

| $V_{Boff}$         | V <sub>B</sub> UVLO Falling Threshold  | - | 5.1 | 5.75 | 6.4 | V |

| V <sub>Bhyst</sub> | V <sub>B</sub> UVLO Hysteresis Voltage | - | -   | 0.5  | -   | V |

# Truth Table

| Missanhau |     | Input | Ou | tput |

|-----------|-----|-------|----|------|

| Number    | HIN | LIN   | НО | LO   |

| 1         | 0   | 0     | 0  | 0    |

| 2         | 1   | 0     | 1  | 0    |

| 3         | 0   | 1     | 0  | 1    |

| 4         | 1   | 1     | 1  | 1    |

| 5         | 0   | Х     | 0  | 0    |

| 6         | 1   | Х     | 1  | 0    |

| 7         | х   | Х     | 0  | 0    |

| 8         | х   | 0     | 0  | 0    |

| 9         | х   | 1     | 0  | 1    |

NOTE:x=floating

**MORNSUN®**

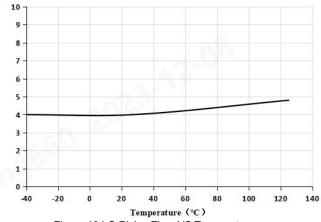

Figure 17 HO Rising Time VS Temperature

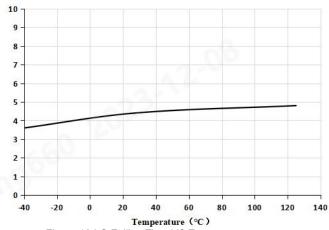

Figure 19 HO Falling Time VS Temperature

TLR (ns)

TLF (ns)

Figure 16 LO Rising Time VS Temperature

Figure 18 LO Falling Time VS Temperature

THE (ns)

Figure 20 Waveform for Rising/Falling Edge Propagation Delay

Figure 21 Waveform for Matching Delay Time

#### **Operating Principle**

SCM3510A is an integrated driver chip that integrates outputs from both high and low side drivers, providing convenience for driving half-bridge and full-bridge circuits.

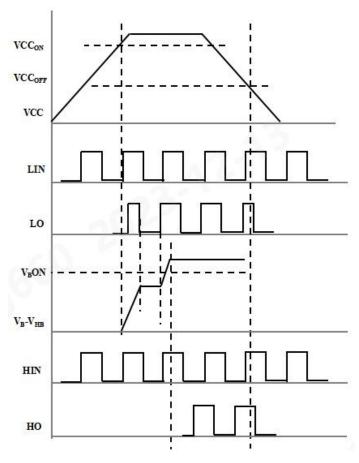

This chip has built-in under voltage protection function, Under voltage lockout(UVLO) is used to prevent erroneous operation during devices startup and shutdown, as well as when the supply voltage of driver is below the specified rated operating voltage range. Both the VCC on the input side and  $V_B-V_{HB}$  on the output side have their own UVLO monitors. The input side of SCM3510A enters under voltage lockout when VCC<VCCOFF. The driver outputs LO and HO remain low when input side of SCM3510A is in the under voltage lockout condition. Each driver output can independently enter under voltage lockout. For example, HO unconditionally enters under voltage lockout when  $V_B-V_{HB}$  is below  $V_BON$ , and exits under voltage lockout when  $V_B-V_{HB}$  rises above  $V_BON$ , as shown in the following figure.

Figure 22 UVLO Sequence Diagram

# **Using Suggestion**

- 1. Connect a 0.1nF, low ESR capacitor near the chip power supply port to reduce interference caused by power fluctuations on the chip(The capacitor should be as close as possible to power supply port of the chip, and it is recommended not to exceed 2mm).

- 2. Unused input and control ports should be pulled up or down. And pins should not be disconnected. In strong interference situation, unconnected pins can easily interfere with the operating of the chip.

- 3. In order to reduce the interference caused by parasitic inductance in the output signal loop on the chip driving signal, the line from HO and LO pins to the MOSFET gate port should be as short as possible.

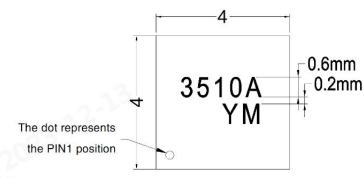

#### Ordering Information

| Product Model | Package    | Pin Number | Screen Printing | Packing    |

|---------------|------------|------------|-----------------|------------|

| SCM3510AGA    | LGA4x4-10L | 10         | 3510A<br>YM     | 5.7k/Plate |

Product model and screen description

SCM3510XYZ:

(1)SCM3510, product code. (2)X = A-Z, version code.

(3)Y = G, package code; G: LGA package.

(4)Z = C, I, A, M, temperature class code; C: 0°C-70°C, I: -40°C-85°C, A: -40°C-125°C, M: -55°C-125°C.

(5)YM: product trace source code; Y: product production year code, M: product production month code.

#### Note:

- 1, Typeface: Arial;

- 2, Character size: Height: 0.6mm, Spacing: 0.1mm, LineSpacing: 0.2mm

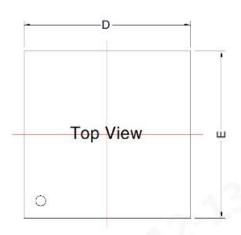

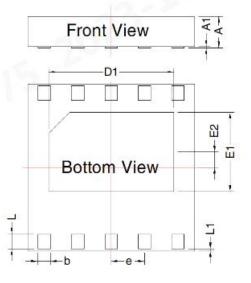

# Package Information

# THIRD ANGLE PROJECTION

|       |          | LGA4x4-10L |                |           |  |

|-------|----------|------------|----------------|-----------|--|

| Monte | Dimens   | ion(mm)    | Dimension(inch |           |  |

| Mark  | Min      | Max        | Min            | Max       |  |

| Α     | 0.70     | 0.80       | 0.028          | 0.031     |  |

| A1    | 0        | 0.05       | 0              | 0.02      |  |

| D     | 4.00     | BSC        | 0.157          | BSC       |  |

| D1    | 2.90     | 3.10       | 0.114          | 0.122     |  |

| E     | 4.00 BSC |            | 0.157          | BSC       |  |

| E1    | 1.80     | 2.00       | 0.071          | 0.079     |  |

| E2    | 0.37     | 0.37 BSC   |                | BSC       |  |

| L     | 0.35     | 0.450      | 0.014          | 0.018     |  |

| L1    | 0.05     | 0.05 BSC   |                | 0.002 BSC |  |

| е     | 0.80     | BSC        | 0.031 BSC      |           |  |

| b     | 0.25     | 0.35       | 0.010          | 0.014     |  |

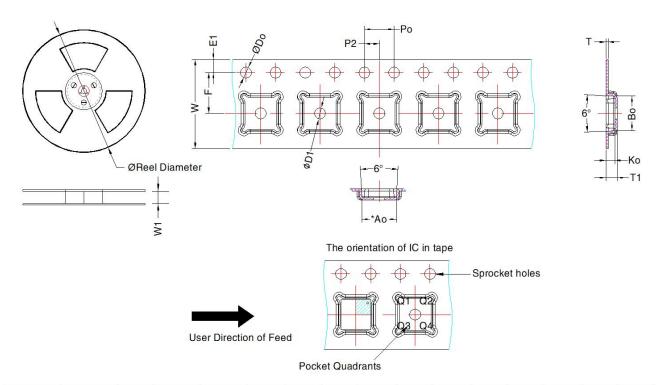

| Device     | Package<br>Type | MPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm)  | B0<br>(mm)  | K0<br>(mm) | T<br>(mm)       | W<br>(mm)  | E1<br>(mm) | F<br>(mm) | P1<br>(mm)    | P0<br>(mm) | D0<br>(mm) | D1<br>(mm)    | Pin1<br>Quadrant |

|------------|-----------------|------|--------------------------|--------------------------|-------------|-------------|------------|-----------------|------------|------------|-----------|---------------|------------|------------|---------------|------------------|

| SCM3510AGA | LGA4x4-10L      | 5700 | 330                      | 12.4                     | 4.47 ± 0.20 | 4.47 ± 0.20 | 1.20 ± 0.3 | $0.30 \pm 0.05$ | 12.0 ± 0.2 | 1.75 ± 0.1 | 5.5 ± 0.1 | $8.0 \pm 0.3$ | 4.0 ± 0.1  | 1.5 ± 0.1  | $1.5 \pm 0.2$ | Q2               |

### NOTE:

The minimum order quantity is the minimum package quantity and the order quantity must be an integer multiple of MPQ.

# Mornsun Guangzhou Science & Technology Co., Ltd.

Address: No. 5, Kehui St. 1, Kehui Development Center, Science Ave., Guangzhou Science City, Luogang District, Guangzhou, P. R. China

Tel: 86-20-3860185

Fax:86-20-38601272

E-mail: info@mornsun.cn www.mornsun-power.com