# **MORNSUN®**

Non-isolated & regulated 40A single output POL Digital Regulators

Patent Protection RoHS

- ASICs, FPGA, ARM

- Network processor

- Al processor

- Distributed power supply

- Communication equipment

- Servers and storage devices

# **FEATURES**

- Wide input voltage range: 4.5-14VDC, including 5V, 12V universal input

- Wide output voltage range: 0.6 to 3.3VDC

- 40A output current

- High output voltage deviation 3mV

- Output ripple as low as 6 mVp-p, 0.6Vout, 100%lo

- PMBus digital communication protocol

- Operating temperature range: -40 °C to +85 °C

- Efficiency up to96.7%, 5Vin, 3.3Vout, 50%lo, loss only 4.5W

- Remote control, PGOOD, remote compensation, clock synchronization functions

- Input under-voltage, output over/under-voltage protection functions

- Output over-current, short circuit, over-temperature protection functions

- Configure and monitor using PMBus

The KD12S-40A digital modules are non-isolated 40A single output POL power supply, it can work in a wide input voltage range of 4.5-14VDC, compatible with front-end 5V/12V input system. It provides an output of precisely adjustable 0.6-3.3VDC voltage through external analog voltage divider, it features PMBus digital control, in addition, it also has PMBus of communication protocol, remote control, PGOOD, remote compensation, clock synchronization, multi-module parallel functions, and with input over/under-voltage, output over/under-voltage, output over-current, short circuit, over-temperature and other protections, the host computer can realize human-computer interaction, it provides a large number of operating instructions to control and monitor the module, and it has the characteristics of high voltage accuracy, low output ripple, and high dynamic response.

Note: ①Use the host computer together, please refer to website for details, and contact FAE for technical support consultation.

| Selection              | Guide          |                          |                |                               |             |                                 |                              |                       |

|------------------------|----------------|--------------------------|----------------|-------------------------------|-------------|---------------------------------|------------------------------|-----------------------|

| Certification Part No. | Part No        | Input Voltage (VDC)      | Output Voltage | Output Voltage Output Current |             | Output Voltage<br>Accuracy (mV) | Efficiency<br>(Nominal, Full | Ripple<br>(Vo=1.0VDC) |

|                        | r an 140.      | Nominal (VDC)<br>(Range) | (VDC)          | (A)<br>Max.                   | Nominal     | Load, Typ.)                     | Nominal,<br>Full Load        |                       |

|                        |                | 12<br>(4.5-14)           | (0.6-1.8)      | 40                            |             | 87.5%                           |                              |                       |

|                        | KD12S-40A      |                          | ±3             |                               | 12mVp-p     |                                 |                              |                       |

|                        | 12<br>(7.5-14) | 3.3                      | 40             |                               | (Vo=1.0VDC) |                                 |                              |                       |

Note:

① The default output of module is 0.6V. For threshold fine-tuning, see PMBus operation Guide. For simulation adjustment, see TRIM adjustment function.

| Limit Rating |                                                     |      |      |      |

|--------------|-----------------------------------------------------|------|------|------|

|              | Parameter                                           | Min. | Max. | Unit |

| Voltage      | VIN                                                 | -0.3 | 15   | V    |

|              | NC, TRIM, PG, CTRL, SHARE3, SHARE1                  | -0.3 | 7    |      |

|              | VS-, VS+, DATA, SMBALERT#, CLK, SYNC, SHARE, SHARE2 | -0.3 | 5.5  | V    |

|              | ADDRESS 0, ADDRESS 1                                | -0.3 | 3.6  |      |

Note:

1. Exceeding the stress values listed in the "Maximum Rating" table may cause permanent damage to the device. The reliability of the device may be affected under the limit rated conditions for a long time. All voltage values are based on GND.

2. The power module can be used in a variety of applications, from simple independent power supply to complex distributed power supply architecture. In order to maintain the maximum flexibility, the internal fuse is not included, but in order to achieve the maximum security and system protection of the system, it is recommended to add a fuse at the input end (maximum rating is recommended to be 35A).

**MORNSUN®**

MORNSUN Guangzhou Science & Technology Co., Ltd.

| Item                                                                               | Operating Conditions                                                             |               |                  | Min. | Тур.        | Max.  | Unit               |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------|------------------|------|-------------|-------|--------------------|

| Input Voltage Range                                                                |                                                                                  |               |                  | 4.5  | 12          | 14    |                    |

|                                                                                    | Through the external resi                                                        | stance divide | er               | 0.6  |             | 3.3   | VDC                |

|                                                                                    | 100% load                                                                        |               | <u> </u>         |      | 20.6        |       |                    |

| Output Current Max.                                                                |                                                                                  |               |                  |      |             | 40    | _                  |

| Output Over-current Protection Threshold                                           | 0.6-3.3                                                                          |               |                  |      | 50          |       | Α                  |

| The PMBus Can Be Used For Adjustment)                                              | Nominal Voltage input. 0                                                         | % load. Vo=0  | 6V               |      | 30          |       |                    |

| Input Current No-load (Module Enabled)                                             | Nominal Voltage input, 0% load, Vo=0.6V  Nominal Voltage input, 0% load, Vo=3.3V |               |                  |      | 220         |       | mA                 |

| Output Voltage Deviation                                                           | Nominal Voltage Input, U% load, Vo=3.3V                                          |               |                  |      | 3           | 20    |                    |

| Linear Adjustment Deviation                                                        |                                                                                  |               |                  |      | 1           | 6     | mV                 |

| ·                                                                                  | Test at 10%lo-100%lo                                                             |               |                  |      | 2           | 10    | •                  |

| Ecodo / Ajasimoni Dovidilon                                                        | 1031 01 10/010 100/010                                                           |               | 0.6VDC           |      | 6           |       |                    |

|                                                                                    |                                                                                  |               | 1.0VDC           |      | 12          |       | -                  |

| Output Voltage Ripple & Noise                                                      | 20Mhz, measurement me                                                            | ethod         | 1.8VDC           |      | 18          |       | mVp                |

|                                                                                    |                                                                                  |               | 3.3VDC           |      | 33          |       | -                  |

|                                                                                    |                                                                                  |               |                  |      |             |       | 5<br>10<br>mV      |

|                                                                                    | 20Mhz, measurement me                                                            |               | 0.6VDC<br>1.0VDC |      | ±18         | ±85   |                    |

| )Vhamic Load                                                                       | 25%-75% load step chanç<br>Voltage input                                         | ge, Nominal   |                  |      | ±36         | ±110  |                    |

|                                                                                    | Co=6x47uf+2x680uF+4x10                                                           | )OuF          | 1.8VDC           |      | ±54         | ±150  |                    |

|                                                                                    |                                                                                  |               | 3.3VDC           |      | ±99         | ±240  | 0, 10              |

| Temperature Coefficient                                                            |                                                                                  |               |                  |      | ±0.4        | 10000 | <b>%/</b> °0<br>μF |

| Capacitive Load(µF) Max.                                                           |                                                                                  | Vo=0.6VDC     |                  | 79.4 | 81.4        | 10000 |                    |

|                                                                                    |                                                                                  |               |                  |      | 87.5        |       | %                  |

| Efficiency                                                                         | Vin=12VDC, 100% load                                                             | Vo=1.0DC      |                  | 85.5 |             |       |                    |

|                                                                                    |                                                                                  | Vo=1.8VDC     |                  | 89.7 | 91.7        |       |                    |

|                                                                                    |                                                                                  | Vo=3.3VDC     |                  | 92   | 94.3        |       |                    |

|                                                                                    |                                                                                  | Vo=0.6VDC     |                  |      | 5.48        |       | _                  |

| LOSS                                                                               | Vin=12VDC, 100% load                                                             | Vo=1.0VDC     |                  |      | 5.71        | -     | w                  |

|                                                                                    |                                                                                  | Vo=1.8VDC     |                  |      | 6.52        |       |                    |

|                                                                                    |                                                                                  | Vo=3.3VDC     |                  |      | 7.98        | -     |                    |

| Module Frequency                                                                   |                                                                                  |               |                  |      | 540         | -     | kHz                |

|                                                                                    | Switching frequency range                                                        | <u> </u>      |                  | 200  |             | 1500  |                    |

| SYNC                                                                               | SYNC high-level threshold                                                        |               |                  | 2.0  | <del></del> | -     | V                  |

|                                                                                    | SYNC low-level threshold                                                         |               |                  |      |             | 0.8   |                    |

|                                                                                    | Minimum SYNC pulse wid                                                           | חוג           |                  | 0.1  |             | 100   | ns                 |

| Remote Control Positive Logic CTRL  Pulled high(Module on)  Pulled low(Module off) |                                                                                  |               | 2.1<br>0         |      | 5<br>0.5    | V     |                    |

|                                                                                    | Pulled high(Module off)                                                          |               |                  | 2.1  |             | 5     |                    |

| Remote Control Neaative Loaic CTRL                                                 | Pulled low(Module on)                                                            |               |                  | 0    |             | 0.5   | V                  |

|                                                                                    | Open threshold                                                                   |               |                  |      | 4.25        |       |                    |

|                                                                                    | Turn Off Threshold                                                               |               |                  |      | 4.0         |       | V                  |

|                                                                                    | PMBus Instruction adjusta                                                        | ıble range    |                  | 4.25 |             | 14    | 1                  |

|                                                                                    |                                                                                  | iolo idiligo  |                  |      | 800         |       |                    |

|                                                                                    | TRIM Threshold                                                                   |               |                  |      | 000         | _     | m۷                 |

# DC/DC Converter KD12S-40A Series

| Output Over-temperature Protection | 13 | ) -         | °C |

|------------------------------------|----|-------------|----|

| Hot Plug                           | L  | Unavailable |    |

| Note:                              |    |             |    |

- 1. This module adopts digital control, which includes a configuration file, which affects the function and performance of the module. Unless otherwise stated, all specifications are in the default configuration file. If the configuration file needs to be changed, please refer to the following PMBus instruction information. The positive and negative logic of the module in the above table can be modified through digital control;

- 2. Unless otherwise stated, the above specifications are tested under the design reference recommendation;

- 3. Unless otherwise stated, the output voltage is tested on the output pin of the product;

- 4. Unless otherwise stated, the above specifications apply to 1.0V output;

- 5. Changing switching frequency will affect module performance. Please confirm with FAE before changing;

- 6. The external synchronous clock pin signal must be a square waveform with a duty cycle of 50%.

- 7. 3.3V linear regulation low voltage is 7.5V.

| Item                                                           |                                                               | Operating Conditions                                               | Min.              | Тур.          | Max.           | Unit       |

|----------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------|-------------------|---------------|----------------|------------|

| Upper Comp                                                     | outer Signal Characteristics                                  |                                                                    |                   |               |                |            |

| Over-tempera                                                   | ture Protection                                               |                                                                    | _                 | 130           |                | $^{\circ}$ |

| PMBus Temper                                                   | ature Control Range                                           |                                                                    | 120               | _             | 160            |            |

| Input Under-vo                                                 | oltage Protection PMBus Adjustable                            | Range                                                              | 4.25              | _             | 13.8           | V          |

| PGOOD Cho                                                      | aracteristics                                                 |                                                                    |                   |               |                |            |

| PGOOD Thresh                                                   | nold Accuracy                                                 |                                                                    | -4                |               | 4              | %          |

| Upper Comp                                                     | outer Measurement Characterist                                | ics                                                                |                   |               |                |            |

| Upper Compu                                                    | rter Output Voltage Measurement Ro                            | ange                                                               | 0.5               | -             | 4.5            | V          |

| Upper Compu                                                    | iter Output Voltage Offset Voltage                            |                                                                    | -                 | 0.1           | -              | <u> </u>   |

| PC Output Vol                                                  | tage Measurement Accuracy                                     | Vo=1V                                                              | -0.8              | -             | 0.8            | %          |

| Upper Compu                                                    | ter Output Current Measurement Ro                             | ange                                                               | 0                 | _             | 50             | Α          |

| Output Current Measurement Deviation of<br>Upper Computer      |                                                               | lo≥20A, IOUT_CAL_GAIN=0.503mΩ                                      | -640              | _             | 640            | mA         |

| Note: The above                                                | e contents are related specifications of PN                   | MBus digital configuration. For details, see App                   | lication recom    | mendation.    |                |            |

| UVLO                                                           |                                                               |                                                                    |                   |               |                |            |

| $V_{\text{IN(on)}}$                                            | Input turn-on voltage                                         | Default settings                                                   |                   | 4.25          |                | V          |

| $V_{IN(off)}$                                                  | Input turn-off voltage                                        | Default settings                                                   |                   | 4             |                | V          |

| $V_{INON(rng)}$                                                | V <sub>INON(rng)</sub> Programmable range for turn on voltage |                                                                    | 4.25              |               | 14             | V          |

| V <sub>INOFF(mg)</sub> Programmable range for turn off voltage |                                                               | 4                                                                  |                   | 13.75         | V              |            |

| Note: Hysteresis                                               | of at least 150 mV is specified by design.                    |                                                                    |                   |               |                |            |

| OUTPUT over                                                    | -voltage / under-voltage                                      |                                                                    |                   |               |                |            |

| $V_{FBOV}$                                                     | Trim pin over voltage threshold                               | Default settings                                                   | -                 | 800           |                | mV         |

| $V_{FBUV}$                                                     | Trim pin under-voltage threshold                              | Default settings                                                   | _                 | 528           | -              | mV         |

| Note: The refere                                               | nce voltage of Trim is 600mV. Before the Ti                   | rim voltage reaches 800mV, the product will tu                     | ırn off the drive | but not enter | the overvoltag | e protecti |

| state (latch off).                                             | After the Trim voltage reaches 800mV, the                     | e product latch off will be turned off.                            |                   |               |                |            |

| PGOOD                                                          | <del>_</del>                                                  | •                                                                  |                   |               |                |            |

| V <sub>FBPGH</sub>                                             | PGOOD high threshold                                          | Default settings                                                   |                   | 642           |                | mV         |

| V <sub>FBPGL</sub>                                             | PGOOD low threshold                                           | Default settinas                                                   |                   | 558           |                | mV         |

| V <sub>PG(acc)</sub>                                           | PGOOD accuracy over range                                     |                                                                    | -4                |               | 4              | %          |

| 1 - 1                                                          |                                                               |                                                                    |                   | -             |                |            |

| V <sub>PG(hyst)</sub> PGOOD hysteresis voltage                 |                                                               | W 9/41 5 4                                                         | 15                | 28            | 45             | mV         |

| R <sub>PGOOD</sub>                                             | PGOOD pull-down resistance                                    | V <sub>FB</sub> =0V, I <sub>PGOOD</sub> =5mA                       | -                 | 50            | -              | Ω          |

| IPGOOD(Ik)                                                     | PGOOD pin leakage current                                     | $V_{\text{Trim}} = 600 \text{ mV}, V_{\text{PGOOD}} = 5 \text{ V}$ | -                 |               | 20             | μ <b>A</b> |

| †PGDELAY                                                       | PGOOD delay time after soft-start sequence is complete        | Default settings                                                   | _                 | 2             |                | ms         |

**MORNSUN®**

MORNSUN Guangzhou Science & Technology Co., Ltd.

| Item                                | Operating Conditions           | Min.                                                                   | Тур.          | Max.         | Unit    |

|-------------------------------------|--------------------------------|------------------------------------------------------------------------|---------------|--------------|---------|

| Operating Temperature               | See temperature derating curve | -40                                                                    |               | 85           | °C      |

| Storage Temperature                 |                                | -55                                                                    |               | 125          |         |

| Storage Humidity                    | Non-condensing                 | 5                                                                      |               | 95           | %RH     |

| Reflow Soldering<br>Temperature*    |                                | Peak temperature Tc $\leq$ 260°C, the maximum time above 217°C is 60 s |               |              | aximum  |

| MTBF                                | MIL-HDBK-217F@25℃              | 18957                                                                  |               | -            | k hours |

| Altitude                            |                                | -                                                                      |               | 2000         | m       |

| Vibration                           |                                | 10-150                                                                 | Hz, 5G, 0.75n | nm. along X, | Y and Z |

| Moisture Sensitivity Level<br>(MSL) | IPC/JEDEC J-STD-020D.1         | MSL 3                                                                  |               |              |         |

| Pollution Degree                    |                                | PD 3                                                                   |               |              |         |

| Mechanical Specific                                     | Mechanical Specifications |  |  |  |  |

|---------------------------------------------------------|---------------------------|--|--|--|--|

| Case Material Open frame                                |                           |  |  |  |  |

| Dimensions                                              | 33.00 x 22.10 x 9.05 mm   |  |  |  |  |

| Weight                                                  | 8.8g(Typ)                 |  |  |  |  |

| Cooling Method Free air convection or forced convection |                           |  |  |  |  |

#### Input Filtering

The module should be connected to a low ACR power supply. An input capacitor must be ensured near the input pin of the module to ensure the stability of the module. To minimize input voltage ripple, ceramic capacitors with ESR and electrolytic/polymer capacitors with low ESR are recommended.

If applied to 4.5V input applications, please follow the following suggestions:

- a. The input voltage of the front stage must be  $\geq$  4.5V;

- B. Recommended for front-end PCB layout: It is recommended to use at least 4oz, width greater than 1cm, length less than 5cm.

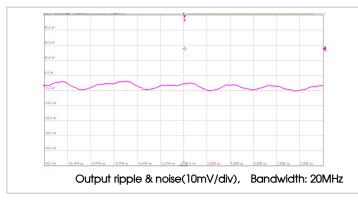

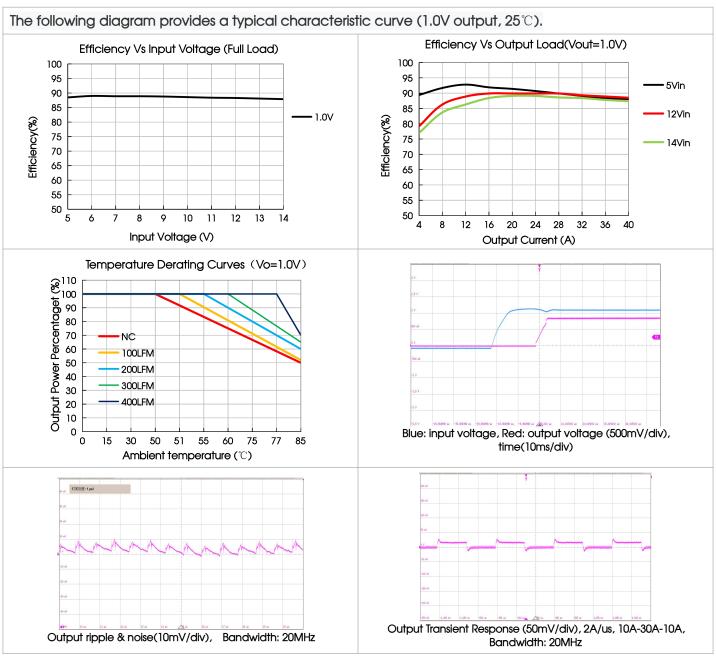

#### **Output Ripple & Noise**

The default loop compensation can be adapted to most application requirements. In addition, the output of the product will have some low-frequency ripple interference, which has nothing to do with the instability of the control loop. The total output ripple and noise of the module can be kept at a low amplitude.

It is recommended to place ceramic capacitors with low ESR and electrolytic/polymer capacitors with low ESR as close to the load as possible and parallel multiple capacitors to lower their ESR. To make capacitors more effective, It is recommended to pay attention to PCB layout and wiring when applying.

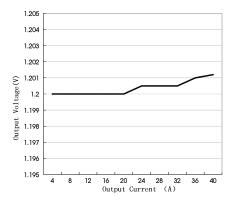

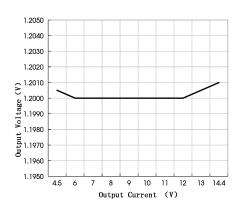

#### Output Accuracy

This module is a high-precision product. The output current is 0-40A, the output voltage is 1.0VDC, and the input is 4.5-14VDC. The typical accuracy curve is:

Load adjustment deviation

Linear adjustment deviation

#### **PMBus Data Format**

PMBus data format

The PMBus command (set threshold, voltage, or exception status) supports three data formats that require literal and numeric representations as parameters (set threshold, voltage, or report such commands). Compatible modules need to support only one of these formats. Modules support only linear data formats for these commands. In this format, the data parameter consists of two parts, mantissa and exponent. The number represented by this parameter can be expressed as:

Value = mantissa x 2exponents

#### **PMBus Address**

On the bus, each PSU must be assigned a unique ADDRESS. 64 addresses (0-63) can be selected through the ADDRESS 1 and ADDRESS 0 pins. The addresses are set in the form of two octal (0-7) digits (0 to 63 in decimal notation), one number per pin. ADDRESS 0 is a low order number. During PMBus communication, PMBus ADDRESS bit '0b' +ADDRESS 1+ADDRESS 0 of the module power supply, and the address setting resistance is shown in the following table:

| number | resistance( $k\Omega$ ) |

|--------|-------------------------|

| 0      | 8.45                    |

| 1      | 16.2                    |

| 2      | 25.5                    |

| 3      | 37.4                    |

| 4      | 54.9                    |

| 5      | 84.5                    |

| 6      | 133                     |

| 7      | 200                     |

Such as:

ADDRESS 1 uses a 37.4K resistor, ADDRESS 0 uses a 37.4K resistor, and the octal value is 33. The actual bit machine displays 27 address bits.

- 1. If the pin resistances of ADDRESS 1 and ADDRESS 1 are out of range, the power module will not continue to respond to PMBus instructions, and the upper computer will not show that the module is detected;

- 2. Other resistance values may cause incorrect PMBus addresses. You are advised to ensure that the resistance values are consistent with the preceding table.

#### Module Startup and Shutdown

The startup and shutdown of the module are jointly controlled by the PMBus Operation instruction, remote Control pin and input voltage.

Note:

If the module is running within the shutdown delay time, avoid opening the module before the shutdown delay time expires. The module is allowed to open only after the shutdown delay time has ended and the module has been turned off. This is also true for applications where two modules are in parallel, the switch delay time of both modules must be configured to the same value.

#### Soft Start

The soft start up time of the module can be configured. The TON\_RISE PMBus command is optional from 600 us to 9 ms. For details, see the command description. When selecting the soft start time, the charging current on the output capacitor should be considered. In applications with a large number of output capacitors, this current will lead to over current protection and shut down the module. Therefore, in order to ensure that these problems do not occur, the charging current of the output capacitor should be considered when considering the setting of the over current threshold. The charging current of the output capacitor can be obtained by the following formula:

$$I_{CAP} = \frac{V_{OUT} \times C_{OUT}}{t_{SS}}$$

- •ICAP is the charging current of the output capacitor (unit: A)

- •VOUT is the output voltage of the module, expressed in V

- •COUT is the total capacity of the output capacitance, expressed in F

- •tSS indicates the selected soft start up time (unit: s)

After calculating the charging current, the over current threshold can be configured as the sum of the maximum load current and the charging current of the output capacitor with a certain margin. The margin required can depend on the particular application, but 25% is recommended.

Note:

When two modules are connected in parallel, the soft start up time of the two modules must be the same.

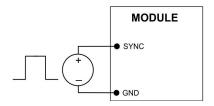

#### Set Frequency and Synchronize Clock

The switching frequency of a module can be synchronized to a signal with an external frequency within a specified range. Add an external clock signal to the SYNC pin of the module as shown in the figure above. The external clock must meet the requirements of the external SYNC signal specified in the electrical specification table.

If this pin is not used, the module should run at the default switching frequency and connect the SYNC pin to GND.

The switching frequency can be synchronized using an external clock on the SYNC pin. When two modules work in parallel, the SYNC signal frequency must be 4 times the switching frequency, and the SYNC signal must be a square waveform with a duty cycle of 50%. The high level threshold should be greater than 2V and the low level threshold should be less than 0.8V. Changes to SYNC and SHARE2 Settings take effect only after the power is restarted.

#### **On-off Delay**

The startup delay time, output voltage rise time and shutdown delay time can be set through the upper computer. More information can be consulted in the PMBus instruction.

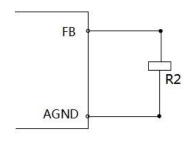

#### Output Voltage Setting

The TRIM pin is connected to the input of the internal error amplifier with an internal reference voltage of  $600 \text{ mV} \pm 0.5\%$ .

$$R2 = R_{FBX}(k\Omega) = \frac{6}{V_O - V_{FB}}$$

| VO(SET) | resistance( $k\Omega$ ) |

|---------|-------------------------|

| 0.6     | OPEN                    |

| 0.9     | 40                      |

| 1.0     | 30                      |

| 1.2     | 20                      |

| 1.5     | 13.33                   |

| 1.8     | 10                      |

| 3.3     | 4.4444                  |

| 4.5     | 3.0791                  |

The module's output voltage can be adjusted using the MFR\_SPECIFIC\_04 (VREF\_TRIM) (D4h) command, which is formatted in a specific\_mfr\_specific\_04 (VREF\_TRIM) (D4h) command. It is adjusted between -20% and 10% of the output voltage. Step by 2mV. In addition, MARGINING and VREF\_TRIM limit the output voltage adjustable range to -30% to 10%, and it is not recommended to exceed this range.

KD12S-40A can determine the actual output voltage through the following three forms:

· No output margin

$$V_{FB} = VREF \_TRIM + 0.6$$

Margin High Voltage State

$$V_{FB} = STEP \_ VREF \_ MARGIN \_ HIGH + VREF \_ TRIM + 0.6$$

· Margin Low State

- VTRIM is the voltage on the TRIM pin

- VREF\_TRIM is the offset voltage of the output voltage

- VREF\_MARGIN\_HIGH is the upper limit of marginal voltage where the output voltage is adjustable

- VREF\_MARGIN\_LOW is the lower limit of marginal voltage where the output voltage is adjustable

#### **PGOOD**

The module will detect the voltage on the TRIM pin to determine whether the output voltage is within the set value range. During the soft start, PGOOD is pulled to the ground. After the soft start, if the output voltage is within the PGOOD threshold range (PG\_LOW to PG\_HIGH), the PGOOD pin will be released after a delay of 2ms. When the output voltage is beyond the PGOOD threshold range, PGOOD will be pulled to the ground immediately. The PGOOD threshold range (PG\_LOW and PG\_HIGH) can be set using the PMBus directive MFR\_SPECIFIC\_07(PCT\_VOUT\_FAULT)PG\_LIMIT.

PGOOD is leak-opening pin, which needs external 10K resistance;

#### **Output over-current Protection**

Output over-current protection, the upper computer can set two response modes, one is self-recovery from short circuit, and the other is module latch after short circuit. The short circuit period is 7 cycles (7 x module output voltage rise time). When two modules are applied in parallel, the over-current protection response of the two channels follows the over-current protection response of the one channel. The two modules must be set in the same over-current protection response mode.

#### **VOUT UV/OV**

The module detects the voltage on the TRIM pins and is used to provide output over-voltage and output under-voltage protection. Both the output over-voltage and output under-voltage thresholds can be set on the PMBus instruction.

Output under-voltage protection works in the same way as over-current protection,

For example, if the IOUT\_OC\_FAULT\_RESPONSE command sets the response to a self-restoring restart, the under-voltage protection response will also be a self-restoring restart. In addition, the under-voltage protection will not detect until the soft boot is complete.

When the output over-voltage protection fault occurs, until the power is restarted or the CNTL is switched over. When the output over-voltage threshold is set to a percentage of the output voltage, the output over-voltage protection is enabled only after the soft boot is complete. When the output over-voltage threshold is set to a fixed value, the output over-voltage protection takes effect continuously. In

parallel applications, ensure that the connection of SHARE1 of the two modules to SHARE1 bus only detects the output under-voltage/over-voltage fault of TRIM1 of module 1 (host), and other channels are not detected. For more information, see MFR\_SPECIFIC\_07 (PCT\_VOUT\_FAULT\_PG\_LIMIT) (D7h) and (E0h) MFR\_SPECIFIC\_16 (COMM\_EEPROM\_SPARE) instruction.

#### VIN UV

Input under-voltage protection can also be set through the upper computer. For details, please refer to VIN\_ON and VIN\_OFF instructions. The default under-voltage is described in the electrical performance table.

#### OT

The module has protection function inside. The upper computer can modify the over-temperature protection point synchronously, which can be set between 120°C and 160°C.

When the internal control IC over-temperature fault (160°C), the PWM of the control IC is turned off. When the temperature drops to 140°C, the PWM restarts.

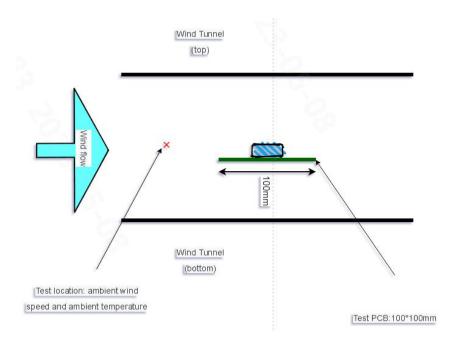

#### Thermal Design

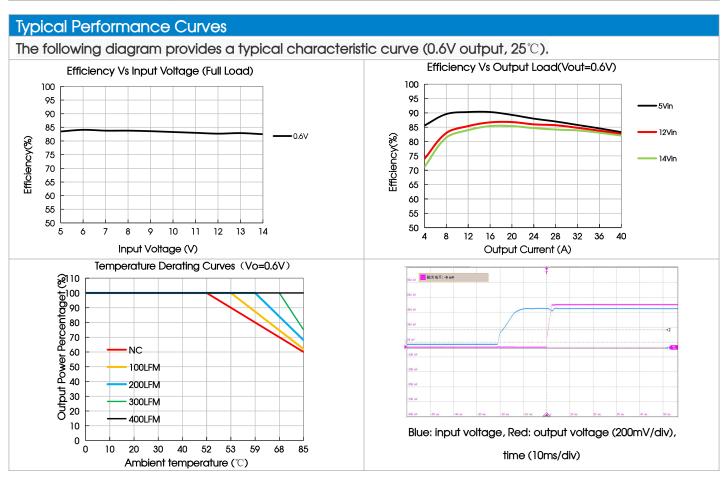

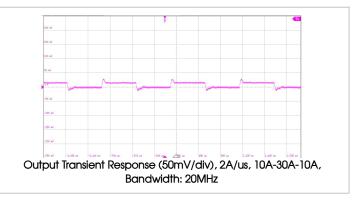

The product can operate in different thermal environments, but sufficient heat dissipation must be provided to ensure reliable module operation. Heat dissipation is mainly realized through the heat conduction from the module pins to the main board and the convective wind speed flowing through the module. The product has a certain degree of derating, but it is not recommended to use over-temperature. The temperature derating curve provides the relationship between the output current and the ambient temperature and wind speed under a specific Vin. See the above table for details.

The module was tested on a 100 x 100mm test plate, installed vertically in a wind tunnel with a cross section of 300 x 203 mm. Also note that the low impedance of the connection between the module and the motherboard effectively reduces the additional power loss.

#### **SHARE1 Fault information**

The SHARE1 pin will be pulled down internally when triggering an over-current, input under-voltage, output over-voltage, output under-voltage, and over-temperature failure. In addition, if the SHARE1 pin of the module is pulled down externally, the module will also shut down.

If the fault response is set to self-recovery, SHARE1 can only be restarted after each channel has been released.

| Fault information | Input<br>under-voltage | Over current                            | Output voltage<br>Under shoot           | output over voltage                                                                                            | over-temperature                                                                  |

|-------------------|------------------------|-----------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Response model    | /                      | Self-recovery or<br>latching can be set | Self-recovery or<br>latching can be set | Latch                                                                                                          | The temperature recovers automatically when it is lower than the enable threshold |

| Pre-soft start up | Turn on                | Turn off                                | Turn off                                | Enable when the threshold is a fixed value or disable when the threshold is a percentage of the output voltage | Turn on                                                                           |

| Soft boot         | Turn on                | Weekly term flow                        | Turn off                                | Enable when the threshold is a fixed value or disable when the threshold is a percentage of the output voltage | Turn on                                                                           |

| After soft boot   | Turn on                | Turn on                                 | Turn on                                 | Turn on                                                                                                        | Turn on                                                                           |

# Use of Remote Compensation and Matters Needing Attention

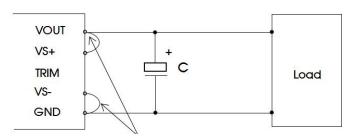

# 1, Remote Sense Application:

The line must be kept as short as possible

#### Note:

- 1) When no remote compensation is used, ensure that VOUT and VS+, GND and VS- are short connected;

- 2) The cable between VOUT and VS+ and GND and VS- should be as short as possible and close to the terminal. Avoid the formation of a large loop area, when noise into this loop, may cause instability of the module.

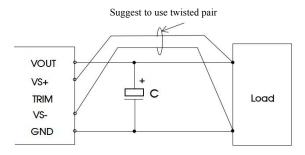

#### 2, Remote Sense Connection used for Compensation:

#### Note:

- 1. If a long remote compensation lead is used, the output voltage may be unstable. If a long remote compensation lead must be used, contact our technical personnel.

- 2. If remote compensation is used, use twisted pair cables or shielded cables and make the leads as short as possible.

- 3. Use wide PCB leads or thick wires between the power module and the load, and keep the line voltage drop lower than 0.3V. Ensure that the output voltage of the power module is within the specified range.

- 4. The impedance of the lead may cause output voltage oscillation or large ripple. Please make adequate evaluation before use.

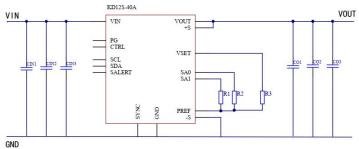

#### Design Reference

#### Application circuit

| Co           | omponents    | Recommended Component Value                                   |

|--------------|--------------|---------------------------------------------------------------|

| CIN1         |              | 2*680uF/35V electrolytic capacitor                            |

| CIN2         |              | 3*22uF/25V ceramic capacitor                                  |

|              | CIN3         | 0.1uFuF/25V ceramic capacitor                                 |

| CO1          | Other output | 0.1uFuF/6.3V ceramic capacitor                                |

| COI          | 3.3V output  |                                                               |

| 600          | 3.3V output  | 6*47uF/6.3V+1*22uF/10V ceramic capacitor                      |

| CO2          | other output | 5*47uF/6.3V+2*22uF/10V ceramic capacitor                      |

|              | 0.6V output  | 1*100uF/25V+3*220uF/25V+1*680uF/35V<br>electrolytic capacitor |

| CO3          | 3.3V output  | 2*680uF/35V electrolytic capacitor                            |

| other output |              | 2*220uF/25V+1*680uF/35V electrolytic<br>capacitor             |

| R1           |              | ODEN                                                          |

| R2           |              | OPEN                                                          |

|              | R3           | 30K                                                           |

Recommended typical application:

VIN: 12V VOUT: 1.0V IOUT: 40A

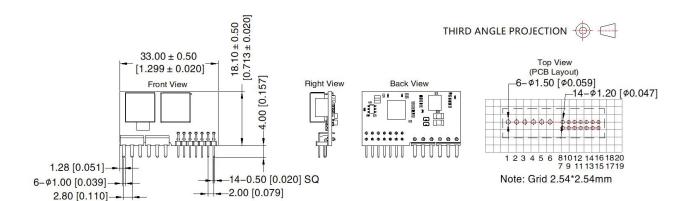

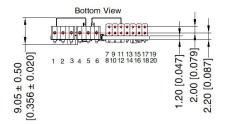

# **Dimensions and Recommended Layout**

Note:

Unit: mm[inch]

Pin diameter tolerances:  $\pm 0.10[\pm 0.004]$ General tolerances:  $\pm 0.25[\pm 0.010]$ The layout of the device is for reference only,

please refer to the actual product

|     | Pin- | -Out |        |

|-----|------|------|--------|

| Pin | Mark | Pin  | Mark   |

| 1   | Vin  | 11   | SDA    |

| 2   | Vin  | 12   | SALERT |

| 3   | GND  | 13   | SA1    |

| 4   | GND  | 14   | SCL    |

| 5   | Vo   | 15   | SYNC   |

| 6   | Vo   | 16   | SA0    |

| 7   | -S   | 17   | CTRL   |

| 8   | +S   | 18   | PG     |

| 9   | NC   | 19   | PREF   |

| 10  | VSET | 20   | NC     |

| PMBus Key Reg             | ister Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPERATION(01h)            | This instruction is used to operate CNTL (CTRL) to turn the module on or off. It can also be used to set the fine setting of the output voltage. The OPERATION of channel 1 register to access the module, PAGE must be set to 0, if the OPERATION of channel to access the module 2 registers, PAGE must be set to 1, if you want to access the channel 1 and channel 2 at the same time, the PAGE must be set to 11. If the channel is configured to machine, the channel can't access the directive, the directive of any written will be ignored, try to read and write any instruction from machine channel will report the fault and trigger SMBALERT. |

| IOUT_CAL_GAIN             | IOUT_CAL_GAIN must equal the actual inductor DCR value to achieve accurate current reading and OC failure protection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Enable and UVLO           | The ON_OFF_CONFIG command is used to select the enable behavior of the converter. In this case, as long as there is the input voltage and higher than the UVLO threshold, whatever state of operations, all use CTRL terminal to enable or disable the converter. If the CTRL terminal dangling through internal 6 mu A current source pull it to 5 v.                                                                                                                                                                                                                                                                                                       |

| TON_RISE                  | Soft start up time Command to set the soft start time. The charging current of the output capacitor should be considered when selecting the soft start time. In some applications (for example, has a large number of output capacitance application), if not properly choose soft start time, then the current may result in wrong jump over current protection circuit.In order to avoid the mistake of jump, when choosing soft start time and over current output capacitor charging current threshold should be included. You can use the formula $I_{CAP} = \frac{V_{OUT} \times C_O}{t_{ss}}$                                                         |

|                           | calculate the charging current of the capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| IOUT_OC_FAULT_LIMIT       | over-current threshold and response order over-current threshold can be set. The module uses the peak current value of the inductor for over-current detection. The current limit should be set to the maximum peak inductor current, plus the output capacitor charging current during start up, plus some load transients and allowance for component changes. The amount of margin required depends on the individual application, for which the maximum peak inductor current is, the design allows for some additional margin, so an over-current threshold of 50A (peak current) is chosen.                                                            |

| IOUT_OC_FAULT_RESP<br>ONE | The IOUT_OC_FAULT_RESPONE command sets the desired overflow event response. In this example, the converter is configured to enter discontinuous mode when an over-current situation occurs. The module can also be configured to latch in the event of an over-current.                                                                                                                                                                                                                                                                                                                                                                                      |

| <b>PMBus</b> | Detail Register  |           |                                                                                                                                                                        |                                                           |                       |

|--------------|------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------------|

| CODE         | COMMAND NAME     | WORD/BYTE | DESCRIPTION: PMBus Command                                                                                                                                             | USER WRITABLE                                             | FACTORY DEFAULT VALUE |

| 00h          | PAGE             | Byte      | Locates separate PMBus command lists in multiple output environments                                                                                                   | YES                                                       | 0XXX XXX0             |

| 01h          | OPERATION        | Byte      | Turn the unit on and off in conjunction with the input from the CONTROL pin. Set the output voltage to the upper or lower MARGIN VOLTAGES.                             | om the CONTROL pin. Set age to the upper or lower YES 0X0 |                       |

| 02h          | ON_OFF_CONFIG    | Byte      | Configures the combination of CONTROL pin input and serial bus commands needed to turn the unit on and off. This includes how the unit responds when power is applied. | YES                                                       | XXX1 0110             |

| 03h          | CLEAR_FAULTS     | Byte      | Clears all fault status registers to 0x00. The "Unit is Off" bit in the status byte is not cleared when this command is issued.                                        | YES <sup>1</sup>                                          | NONE                  |

| 10h          | WRITE_PROTECT    | Byte      | Prevents unwanted writes to the device.                                                                                                                                | YES                                                       | 000X XXXX             |

| 15h          | STORE_USER_ALL   | Byte      | Saves the current configuration into the User Store. Note: This command writes to Non-Volatile Memory.                                                                 | YES <sup>1</sup>                                          | NONE                  |

| 16h          | RESTORE_USER_ALL | Byte      | Restores Store. all parameters to the settings saved in the User                                                                                                       | YES <sup>1</sup>                                          | NONE                  |

| 19h          | CAPABILITY       | Byte      | PEC,SPD,ALRT                                                                                                                                                           | No                                                        | 1011 0000             |

| 20h          | VOUT_MODE        | Byte      | Read-Only Mode Indicator. The data format is linear with an exponent of -9                                                                                             | No                                                        | 0001 0111             |

| 35h          | VIN_ON           | Word      | Sets the value of the input voltage at which the unit should start power conversion                                                                                    | YES 1111 0000 C                                           |                       |

| 36h | VIN_OFF                    | Word | Sets the value of the input voltage at which the unit should                   | YES  | 1111 0000 0001 0000 |

|-----|----------------------------|------|--------------------------------------------------------------------------------|------|---------------------|

|     |                            |      | stop power conversion.                                                         |      |                     |

| 38h | IOUT_CAL_GAIN              | Word | Sets the ratio of the voltage at the current sense pins to the sensed current. | YES  | 1000 0000 0010 0001 |

| 39h | IOUT_CAL_OFFSET            | Word | Nulls any offsets in the output current sensing circuit                        | YES  | 1110 0000 0000 0000 |

|     |                            |      | Sets the value of the output current, in amperes, that causes                  |      |                     |

| 46h | IOUT_OC_FAULT_LIMIT        | Word | the over-current detector to indicate an over-current fault condition.         | YES  | 1111 1000 0001 1110 |

|     |                            |      |                                                                                |      |                     |

| 47h | IOUT_OC_FAULT_RESP<br>ONSE | Byte | Instructs the device on what action to take in response to an                  | YES  | 0000 0111           |

|     |                            |      | output over-current fault.                                                     |      |                     |

| 4Ah | IOUT_OC_WARN_LIMI          | Word | Sets the value of the output current that causes an output                     | YES  | 1111 1000 0011 0010 |

| 451 | OT 54447 4447              |      | Over-current warning                                                           | 1/50 | 0000 0000 1000 0010 |

| 4Fh | OT_FAULT_LIMIT             | Word | over-temperature fault threshold                                               | YES  | 0000 0000 1000 0010 |

| 5lh | OT_WARN_LIMIT              | Word | over-temperature warning threshold                                             | YES  | 0000 0000 01111000  |

| 61h | TON_RISE                   | Word | Target soft-start rise time                                                    | YES  | 1110 0000 0010 1011 |

| 78h | STATUS_BYTE                | Byte | Single byte status indicator                                                   | No   | 0x00 0000           |

| 79h | STATUS_WORD                | Word | Full 2-byte status indicator                                                   | No   | 0000 0000 0x00 0000 |

| 7Ah | STATUS_VOUT                | Byte | Output voltage fault status detail                                             | No   | 0000 0000           |

| 7Bh | STATUS_IOUT                | Byte | Output current fault status detail                                             | No   | 0000 0000           |

| 7Dh | STATUS_TEMPERATURE         | Byte | Temperature fault status detail                                                | No   | 0000 0000           |

| 7Eh | STATUS_CML                 | Byte | Communication, memory, and logic fault status detail                           | No   | 0000 0000           |

| 80h | STATUS_MFR_SPECIFIC        | Byte | Manufacturer specific fault status detail                                      | No   | 0000 0000           |

| 8Bh | READ_VOUT                  | Word | Read output voltage                                                            | No   | 0000 0000 0000 0000 |

| 8Ch | READ_IOUT                  | Word | Read output current                                                            | No   | 1110 0000 0000 0000 |

| 8Eh | READ_TEMPERATURE_<br>2     | Word | Read off-chip temp sensor                                                      | No   | 1111 0000 0110 0100 |

| 98h | PMBUS_REVISION             | Byte | PMBus Revision Information                                                     | No   | 0001 0001           |

| D0h | MFR_SPECIFIC_00            | Word | User scratch pad                                                               | YES  | 0000 0000 0000 0000 |

| D4h | MFR_SPECIFIC_04            | Word | VREF_TRIM                                                                      | YES  | 0000 0000 0000 0000 |

| D5h | MFR_SPECIFIC_05            | Word | STEP_VREF_MARGIN_HIGH                                                          | YES  | 0000 0000 0001 1110 |

| D6h | MFR_SPECIFIC_06            | Word | STEP_VREF_MARGIN_LOW                                                           | YES  | 1111 1111 1110 0010 |

| D7h | MFR_SPECIFIC_07            | Byte | PCT_VOUT_FAULT_PG_LIMIT                                                        | YES  | XXXX XX10           |

| D8h | MFR_SPECIFIC_08            | Byte | SWQUENCE_TON_TOFF_DELAY                                                        | YES  | 111X 000X           |

| E0h | MFR_SPECIFIC_16            | Word | COMM_EEPROM_SPARE                                                              | YES  | 1011 0001 xxxx x011 |

| E5h | MFR_SPECIFIC_10            | Word | IC options                                                                     | YES  | 0111 1111 0000 0000 |

|     |                            |      | ,                                                                              |      |                     |

| E6h | MFR_SPECIFIC_22            | Word | PWM_OSC_SELECT                                                                 | YES  | 0000 0000 0000 0001 |

| E7h | MFR_SPECIFIC_23            | Word | Paged and Common MASK_SMBALERT                                                 | YES  | 0000 0000 0000 0000 |

| EFh | MFR_SPECIFIC_30            | Word | Temperature offset                                                             | YES  | 1111 1000 0000 0000 |

| F0h | MFR_SPECIFIC_32            | Word | API options                                                                    | YES  | 0000 0000 0000 0000 |

| FCh | MFR_SPECIFIC_44            | Word | Device code, unique code to id part number                                     | No   | 0000 0001 1110 0000 |

NOTE 1: No data bytes are sent, only the command code is sent.

# PAGE(00h)

|   | Format      | Unsigned binary integer                                                                                                                           |

|---|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Description | The PAGE command provides the ability to configure, control, and monitor through only one physical address both channels (outputs) of the device. |

| Ī | Default     | 0XXX XXX0 (binary)                                                                                                                                |

|     | PAGE |   |   |   |   |   |     |  |

|-----|------|---|---|---|---|---|-----|--|

| r/w | r    | r | r | r | r | r | r/w |  |

| 7   | 6    | 5 | 4 | 3 | 2 | 1 | 0   |  |

| PA  | X    | Χ | X | X | Х | Х | P0  |  |

| Bits | Field Name | Description                                                                                            |

|------|------------|--------------------------------------------------------------------------------------------------------|

|      |            | 00: (Default) All commands address the first channel.                                                  |

|      |            | 01: All commands address the second channel.                                                           |

| 7,0  | PA,P0      | 10: Illegal input-ignore this write, take no action.                                                   |

|      |            | 11: All commands address both channels.                                                                |

|      |            | If PAGE = 11, any then read commands point to PAGEO always.                                            |

| 6:1  | Х          | X indicates writes are ignored and reads are 0. Any values written to read-only registers are ignored. |

# OPERATION (01h)

| Format      | Unsigned binary integer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | The OPERATION command is used to turn the device output on or off in conjunction with the input from the CNTLx pin (where $x = 1$ for channel 1 and $x = 2$ for channel 2). It is also used to set the output voltage to the upper or lower MARGIN levels.                                                                                                                                                                                                                                                                                                                                                  |

| Description | OPERATION is a paged register. In order to access OPERATION register for channel 1 of the device, PAGE must be set to 0. In order to access OPERATION register for channel 2 of the device, PAGE must be set to 1. For simultaneous access of channels 1 and 2, PAGE command must be set to 11. If the channel is configured as a SLAVE, this command can not be accessed for that channel. Any writes to the SLAVE channel for this command are ignored. An attempt to read and write the SLAVE channel command results in a NACK'd command and the reporting of an IVC fault and triggering of SMB_ALERT. |

| Default     | 0X0000XX (binary)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| r/w | r | r/w    | r/w | r/w | r/w | r | r |

|-----|---|--------|-----|-----|-----|---|---|

| 7   | 6 | 5      | 4   | 3   | 2   | 1 | 0 |

| On  | 0 | Margin |     |     | Х   | Х |   |

| Bits | Field Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | On         | The On bit is used to enable to IC via PMBus. The necessary condition for this bit to be effective is that the cmd bit in the ON_OFF CONFIG register is set high. However, the cmd bit being high is not a sufficient condition to enable the IC via the On bit, as specified below:  0: (Default) The device output is not enabled via PMBus.  1: The device output is enabled if:  a. The supply voltage VIN is greater than the VIN_UVLO threshold, the cmd bit is high, and b. The bit cpr in the ON_OFF CONFIG register is low, or  c. The bit cpr is high and the CNTL_EN pin is enabled (high or low). |

| 6    | 0          | X: Default                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5:2  | Margin     | If Margin Low is enabled, load the value from the STEP_VREF_MARGIN_LOW command. If Margin High is enabled, load the value from the STEP_VREF_MARGIN_HIGH command. (See PMBus specification for more information) 0000: (Default) Margin Off 0101: Margin Low (Ignore Fault) 0110: Margin Low (Act On Fault) 1001: Margin High (Ignore Fault) 1010: Margin High (Act On Fault) Note: Any values written to read-only registers are ignored.                                                                                                                                                                    |

| 1:0  | х          | XX: Default X indicates writes are ignored and reads are 0. Any values written to read-only registers are ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $\bigcirc$ N | OFF | CONF |      | (USP) |

|--------------|-----|------|------|-------|

| ON           | OFF | CON  | י טו | UZII  |

| Format      | Unsigned binary integer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | The ON_OFF_CONFIG command configures the combination of CONTROL pin input and serial bus commands needed to turn the unit on and off.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Description | ON_OFF_CONFIG is a paged register. In order to access this register for channel 1 of the device, PAGE must be set to 0. In order to access this register for channel 2 of the device, PAGE must be set to 1. For simultaneous access of channels 1 and 2, PAGE command must be set to 11. If the channel is configured as a SLAVE, this command can not be accessed for that channel. Any writes to the SLAVE channel for this command are ignored. An attempt to read and write the SLAVE channel command results in a NACK'd command and the reporting of an IVC fault and triggering of SMB_ALERT. |

|             | However, note that page 0 (channel 1) fault status bits (and associated smbalert state) should be capable of being cleared by toggling CNTL1 pin even if channel 1 is a slave. If channel 2 is a slave, then CNTL2 pin is disabled but toggling the CNTL1 pin should also clear page 1 (channel 2) fault status bits and related smbalert state. (The is recommendation is to tie together CNTL1 pins of both devices in a multi-phase configuration).                                                                                                                                                |

| Default     | XXX10110 (binary)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Bolduli     | The default power-up state can be changed using the STORE_USER_ALL command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |   |   | r/w <sup>E</sup> | r/w <sup>E</sup> | r/w <sup>E</sup> | r/w <sup>E</sup> | r   |

|---|---|---|------------------|------------------|------------------|------------------|-----|

| 7 | 6 | 5 | 4                | 3                | 2                | 1                | 0   |

| Х | X | Х | pu               | cmd              | cpr              | pol              | сра |

| Bits | Field Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |